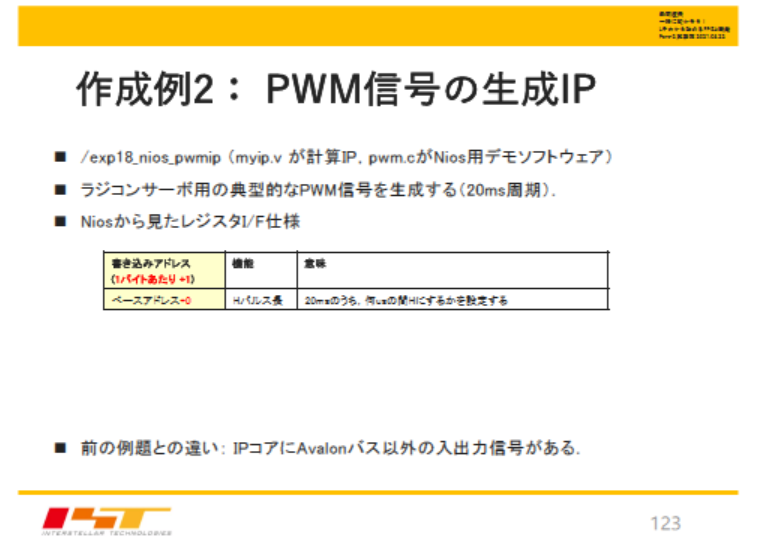

FPGAキット DE10入門 PWM信号生成回路IP

avalonバスに独自I/Oを追加

PWM信号生成IPとAvalonバスの利用

|

|---|

|

図1 FPGAの標準インターフェースAvalonバスを利用すれば,独自IPを作りシステム統合できる.動画では,Avalonバスを介してレジスタを操作し,外部端子からPWM信号を出力するHDLソースを示す.

画像クリックで動画を見る.または記事を読む.[提供・著]森岡 澄夫 |

FPGA開発の初期段階では,基板上のリソースを活用して具体的な回路設計を行い,インターフェースを通じてソフトウェアとの連携を実現することが重要です.

Avalonバスを活用した独自IPの設計と接続

Avalonバスは,FPGA設計における標準的なインターフェースで,設計者が柔軟に独自のIPを作成し,システム全体に統合することを可能にします.次の手順で独自IPを設計します.

IPコアの作成

IPコアはVerilogを用いて記述します.Avalonバスから送られるアドレス(`avs_s1_address`)に基づいてレジスタを更新し,計算結果を返す構造をもつ回路を設計できます.重要な信号には,リセット信号($csi_global_reset$)やクロック信号($csi_global_clk$)があります.

レジスタとインターフェースの設計

入力されるデータを処理するため,ライトアクセス時には`writedata`信号を用いて内部レジスタを更新します.一方,リードアクセス時には`readdata`信号を通じて結果を返します.次のような構造が典型的です.

- アドレス`+0`

レジスタ$r_0$に書き込みまたは読み出し - アドレス`+4`

レジスタ$r_1$の管理

エラーの解消とIP登録

作成したIPコアを`Platform Designer`で登録し,信号の関連付け(Associated ResetやClock)を修正することで,ツールが正しく認識するように設定します.

PWM信号生成の設計

PWM信号は,サーボモータの制御などに使用される信号で,周期とデューティ比を設定することで動作を制御できます.この設計では,Avalonバスを介してレジスタを操作し,外部端子からPWM信号を出力します.

PWM信号生成の基本構造

- PWM出力端子(`pwm_out`)を宣言

- レジスタ操作により,20ms周期内のHigh期間を設定

ソフトウェアによる制御

Avalonバス経由で設定するパラメータをC言語で操作します.たとえば,次のコードによりHigh期間を変化させることが可能です:

“`c

IO(MYIP_0_BASE) = 1500; // 1.5ms

usleep(10000);// 10秒待機

IO(MYIP_0_BASE) = 1000; // 1.0ms

usleep(10000);// 10秒待機

“`

オシロスコープでの波形確認

実際に波形を観測することで,PWM信号の正確性を確認します.この実験では,1.5ms, 1.0ms, 2.0msのHigh期間を順次出力する動作が確認できます.

FPGAの標準通信バス “Avalon”

AvalonバスはFPGA設計における主要なインターフェース規格で,マスタ・スレーブ方式のシンプルな通信モデルを提供します.このバスを活用することで,柔軟かつ効率的なデータ通信を実現できます.

アドレスとデータ

バス通信では,アドレス($avs_s1_address$)を基にデータを送受信します.アドレスは32ビット幅で,ソフトウェアが直接制御可能です.

リード・ライト操作

- リード(`avs_s1_read`):指定アドレスのデータを返却

- ライト(`avs_s1_write`):指定アドレスにデータを送信

タイミングの重要性

クロック信号($csi_global_clk$)と同期して操作が行われるため,タイミング設計が正確である必要があります.

実践的な応用例

Avalonバスを活用することで,次のような高機能IPを効率よく実現可能です.〈著:ZEPマガジン〉

- CRC計算回路の設計

- 各種信号処理IPのシステム統合

- ソフトウェアからの簡単な制御

著者紹介

- NTT,IBM,Sony,NECの各研究所において高性能回路IPやハイレベル・シンセシスの研究,およびプレイステーションなどの製品用SoC開発に従事した後,現職にて民間宇宙ロケットの飛行制御コンピュータの研究開発に従事.FPGAや高位合成を活用している

著書

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD/KIT]Tiny FPGA実習!高校生から始めるHDLプログラミング,ZEPエンジニアリング株式会社.

- [VOD/Pi KIT]カメラ×ラズパイで一緒に!初めての画像処理プログラミング,ZEPエンジニアリング株式会社.

- スパコンでも破れない!高セキュリティ・マイコン・プログラミング,ZEPエンジニアリング株式会社.

- [YouTube]宇宙軌道ロケット 成功の方程式

- [YouTube]宇宙ロケットの電子回路開発

- FPGA/Zynqで作るカスタム・コンピュータ・チップ,ZEPエンジニアリング株式会社.

- Lチカ入門!ソフトウェア屋のためのHDL事はじめ,ZEPエンジニアリング株式会社.

- USBカメラの動画キャプチャ&描画用 Pythonプログラム,ZEPエンジニアリング株式会社.

- ライブラリ完備!組立式ラズパイI/O増設ボード MCC DAQ HATSファミリ誕生,ZEPエンジニアリング株式会社.

参考文献

- [VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門,ZEPエンジニアリング株式会社.