低雑音&高効率!LLC絶縁トランスの定数設計法

ボビン選びから1次/2次の巻き数,共振用インダクタとキャパシタまで

- 著者・講師:並木 精司(Seiji Namiki),パワーアシストテクノロジー株式会社

- 企画・編集:ZEPエンジニアリング株式会社

- 6月29日~7月5日 キット付きウェビナ開催!:一緒に作る!LLC絶縁トランス×超高効率・低雑音電源 完全キット

- 関連製品:[VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】

- 関連製品:[VOD]Pythonで学ぶ マクスウェル方程式 【電場編】+【磁場編】

- 関連製品:[VOD/KIT] ポケット・スペアナで手軽に!基板と回路のEMCノイズ対策 10の定石

- 関連製品:[VOD]事例に学ぶ放熱基板パターン設計 成功への要点

- 関連製品:[VOD]Linux搭載USBマルチ測定器 Analog Discovery Proで作る私の実験室

- 関連動画:[動画]初めての電源・アナログ回路設計[DC-DC コンバータの製作]

- 関連動画:[動画]【実験Before After】プリント基板の見方・描き方・作り方

- 関連動画:[YouTube]電子回路の素[トランジスタ編]

- 関連動画:[YouTube]高校数学からはじめる「ベクトル解析」

LLCコンバータが普及した背景

PFC義務化で,低雑音・高効率な“LLC”が注目される

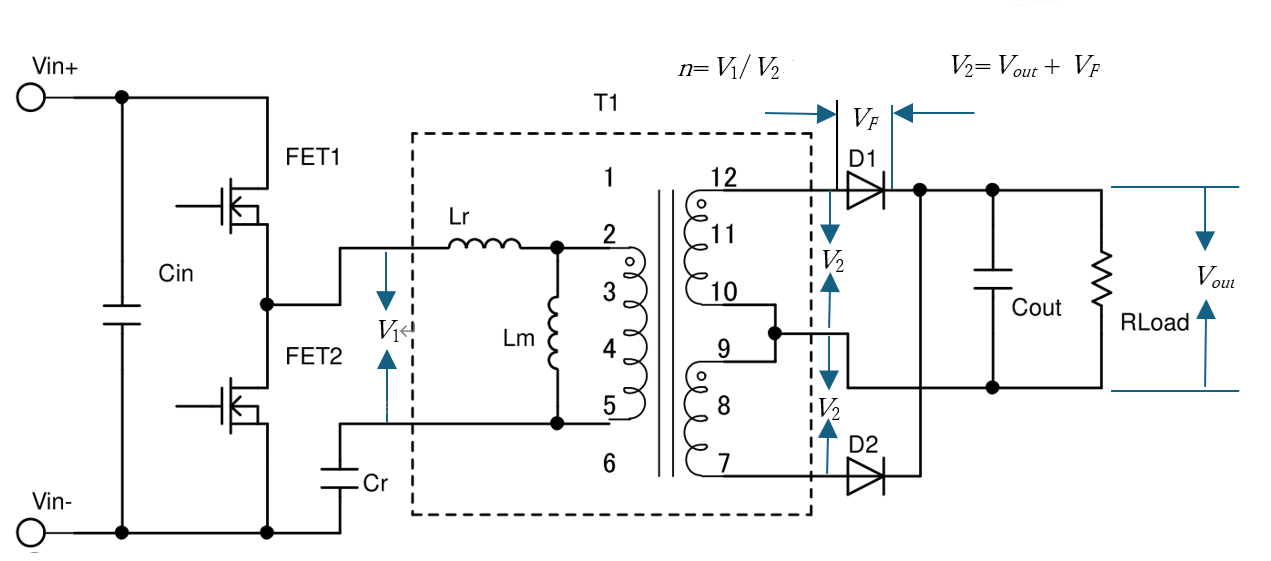

低雑音で高効率,小型で高出力などの特徴をもつDC-DCコンバータ「LLCコンバータ」(図1)の設計法を解説するコンテンツが雑誌やネット上に多く見られるようになりました.

背景には,1994年欧州のIEC規格“IEC61000-3-2”にて,電源環境の改善を目的に高調波規制が始まったことが挙げられます.規制の内容は,入力電力が75Wを超える電子機器の電源は,力率改善回路(PFC,Power Factor Correction)の搭載義務でした.

LLCコンバータは,古くから知られていましたが,電圧変動に弱いという欠点がありました.一方,PFC回路の出力電圧(直流)は,比較的安定化されています.PFC回路が前段に入ることで,LLCコンバータの短所がカバーされ,効率とノイズ特性が良いというソフト・スイッチングの長所が生きることになりました.安全規格が要求する「絶縁距離」も,ボビンの構造で,簡単,確実に確保できます.

使わない理由のなくなったLLCコンバータは,爆発的に普及しました.特に出力電力が比較的に大きい液晶テレビへの採用で普及に拍車がかかりました.

鍵は「トランス設計」

LLCコンバータ用のスイッチング・トランスには,「分割ボビン」を使います.

共振要素になる共振インダクタンスをトランス内部に包括する構造になっていて,多くのDC-DCコンバータが嫌う「漏洩インダクタンス」を積極的に利用します.

LLCコンバータ用のスイッチング・トランスの性能は,鍵を握るボビンの構造設計の良否に大きく依存します.分割ボビンは,外販品が少ないです.ありものを利用して,巻き線で工夫せざるを得ないことも多いです.

出力電圧12V,出力電力数百WのLLCコンバータを作ろうとすると,2次側巻き数がたったの2ターンという計算結果になり,$\phi$0.1の600本撚りのリッツ・ワイヤを巻かなければならない事例もあります.とにかく,LLCコンバータ用のトランスの巻き線作業には,常にノウハウが求められます.

LLCトランスの設計の流れ

STEP1 ボビンを決める

共振インダクタンスはボビンの形状で決まる

初めにボビンを選びます.

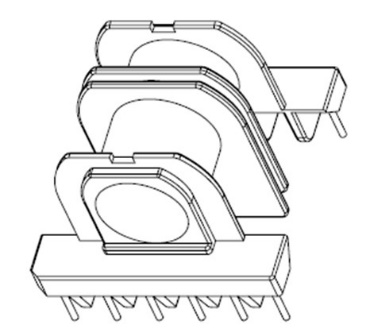

図2に示す「リーケージ・インダクタンス・トランス」用の分割タイプのボビンを使うことが決まっている場合,共振インダクタンスは,そのボビンの物理的な寸法で一義的に決まります.

使うトランスのサイズとボビンが決まってない段階で,共振インダクタンスや共振コンデンサを計算するのは本末転倒です.何よりもまず,LLCコンバータの出力容量に最適なコア・サイズとそのボビンを選ぶことが最優先です.なお,パワーアシストテクノロジー株式会社では,ETD34,ETD39,EER40のボビンを中国から直接輸入して取り揃えています.

|

|---|

| 図2 分割ボビンの外観(ETD34) |

入手性は良くない

LLCコンバータ向けのリーケージ・トランス用ボビンは,秋葉原や通販などで,個人向けに販売されることはありません.

通常,電源メーカやトランス・メーカが自社用に金型を製作して,特定の客先に販売されます.自作したいなら,知り合いのトランス・メーカに,こちらからボビン・サンプルを提供して,試作をお願いするしかありません.

LLCコンバータに使う分割ボビン・トランスには,リーケージ・インダクタンスを稼げる,コアの中足の長い“EER”,“ETD”タイプを採用することが多いです.

少ない技術文献

必要な出力電力に適したボビンのサイズとコアの求め方を解説する技術資料は多くありません.

「スイッチング電源用フェライトテクニカル・データ(TDK,2004年版)」に,100kHzで動作するフォワード・コンバータにおける「標準的な最大出力電力とトランスのトータル損失および温度上昇」の算出曲線が掲載されていたぐらいです.

残念ながらTDK社は現在,温度上昇に関するデータを公開していません.親切のために参考値として掲載したところ,「実際と合わない」と意見が寄せられたのかもしれません.

計算で推定することは「不可能」とは言いませんが,それだけ時間をかけた結果がどの程度役に立つかが微妙です.というのも,例えば,トランスの温度上昇1つをとっても,その計算方法を解説する文献は,私の知る限りないからです.現状,現場の電源設計者は,今までの自分の経験や先輩の知見に頼って決めています.

STEP2 1次巻き数$n_1$を算出

1次側の印加電圧$V_1$(ハーフ・ブリッジの場合,入力DC電圧の1/2)と動作周波数$f_{sw}$,コアの断面積 $A_e$,および適切な磁束密度$B_m$(120m~180mT)から,1次巻き数$n_1$を求めます.

STEP3 1次側を巻き線する

トランスの利用率が最大になるように巻きます.分割ボビンの1次側の巻き窓いっぱいにできるだけ太いリッツ・ワイヤで巻き線します.

STEP4 巻き線比と2次巻き数$n_2$を算出

1次電圧$V_1$と2次電圧$V_2$($=出力電圧 V_{out}+V_F$)から,巻き線比 $n=V_2/V_1$,そして2次巻き数$n_2$を計算します.計算で求まる2次巻き数は,中途半端な値になりますが,一番近い整数の巻き数に丸め(四捨五入)します.

STEP5 2次巻き数から1次側巻き数を求める

2次巻き数から巻き線比を変えないように,1次側巻き数を逆算します.逆算した1次巻き数が変わると,磁束密度も変わります.

コア・サイズが大きく,かつ出力電圧が低く周波数が高い場合は,2次巻き数が“2”になる場合があります.1次入力電圧が低い場合は,1次巻き数も少なくなります.このように巻き数が少ないと,たったの1ターンの違いが全体に大きく影響し,適正な巻き線比に設定することが困難です.

STEP6 2次側を巻き線する

2次側がセンタ・タップ整流の場合は,$n_2$を「2回路分バイファイラ巻き」します.

2次側巻き窓いっぱいになるように,できるだけ太いリッツ・ワイヤで巻き線します.

鉄心を挿入して,鉄心の中足をダイヤモンドやすりで少しずつ削りながら,目標の1次インダクタンスになるように調整します.

STEP7 2次側の全引き出し線をショートする

完成したスイッチング・トランスの2次側巻き線の全部の引き出し線をすべてはんだで完全にショートします.

STEP8 1次側巻き線のショート・インダクタンスを測る

1次側巻き線のショート・インダクタンスを測定します.

STEP9 共振コンデンサ$C_R$を求める

1次インダクタンス$L_P$とショート・インダクタンス$L_S$の実測値がわかったら,目標の共振周波数$f_R$になるように,共振コンデンサ$C_R$の値を計算します.

計算値に一番近い標準容量値を選択します.

STEP10 シミュレーションで制御外れがないか確認する

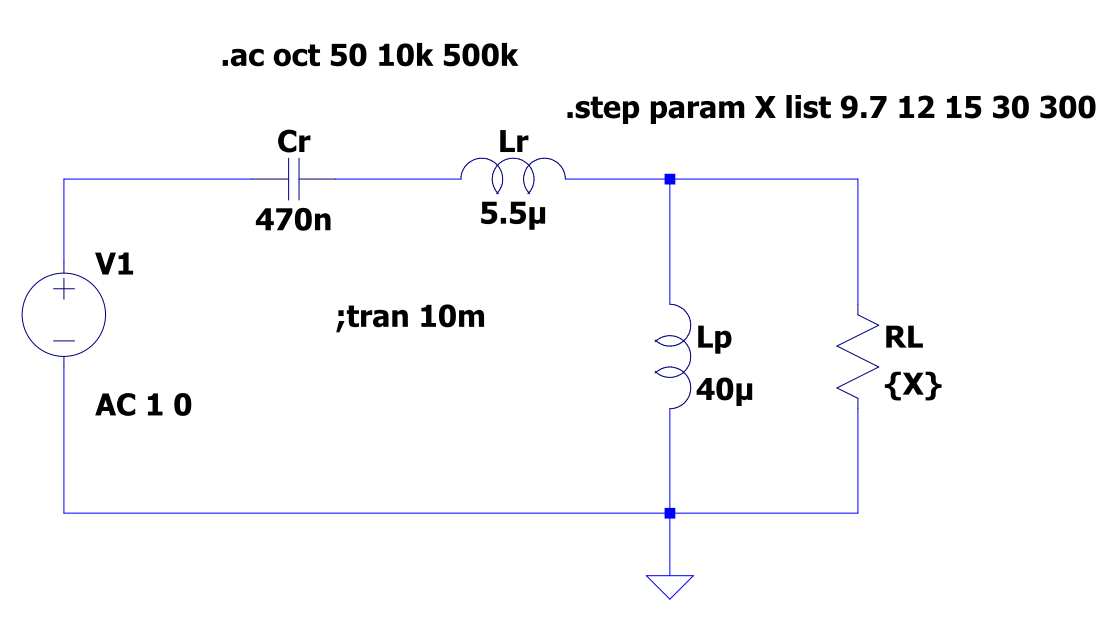

共振インダクタンスと共振キャパシタンスが決まったら,電子回路シミュレータ LTspiceに等価回路(図3)を入力して,伝達特性を解析して表示します(図4).

入力電圧や負荷抵抗の全変動範囲における周波数の変化をチェックします.

最大負荷&最小入力時に,十分な昇圧ゲインがあり,かつ動作周波数が共振のピークを越えていないかを確認します.続いて,最大入力&最小負荷時に,制御可能かどうかも確認します.

制御範囲を超えそうな計算結果が得られたら,$L_m/L_r$比(励磁インダクタンスと漏れインダクタンスの比)とトランスの巻き線比 $n$を調整して,全入力負荷範囲で制御可能になるように調整します.

|

|---|

| 図3 LLCトランスの等価回路.電子回路シミュレータ LTspiceで伝達関数を計算する |