Access:2,144

[VOD/KIT]GPSクロック・ジッタ・クリーナ

100k~700MHz,精度-10乗!非同期で動く送受信機のディジタル通信を可能にする

2023年4月15日

|

|---|

- 型名:z-pptgen-on1

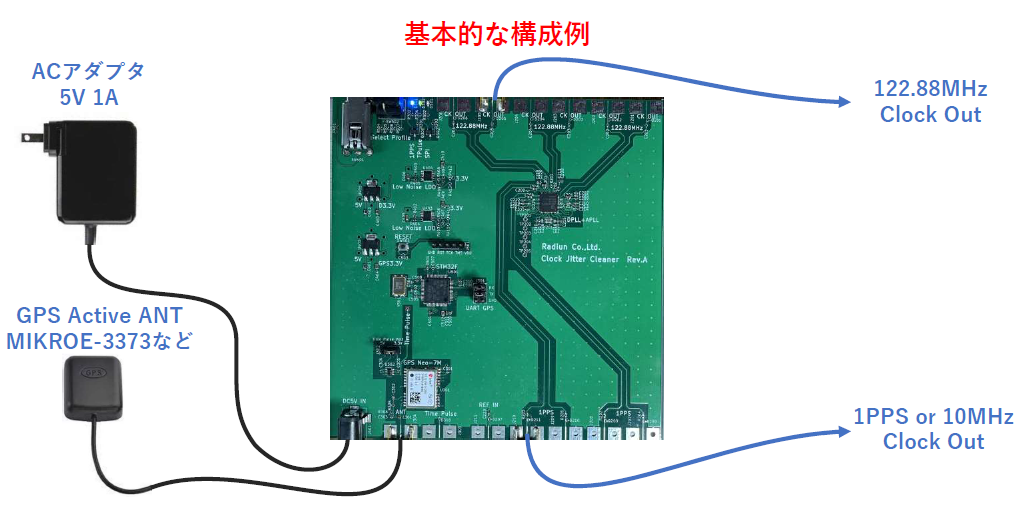

- 仕様:受注生産品,講義280分,解説82頁,GPSアンテナ,ACアダプタ,出力周波数:1PPS,10MHz,30.72MHz,61.44MHz,122.88MHz

- 定価:396,000円(税込・送料無料)

- 開発:株式会社ラジアン(加藤 隆志/Takashi kato)

- 企画編集・主催: ZEPエンジニアリング株式会社

- 関連製品:[KIT]ミリ波5G対応アップ・ダウン・コンバータ MkⅡ

- 関連製品:[KIT]実験用28GHzミリ波パッチ・アンテナ

- 関連製品:[KIT]実験用800M~6GHz 広帯域90°ハイブリッド

- 関連製品:[VOD]MATLAB/Simulink×FPGAで作るUSBスペクトラム・アナライザ

- 関連製品:[VOD/KIT]3GHzネットアナ付き!RF回路シミュレーション&設計・測定入門

- 関連製品:[VOD/KIT]3GHzネットアナ付き!初めてのIoT向け基板アンテナ設計

- 関連製品:[VOD/KIT]初めてのソフトウェア無線&信号処理プログラミング 基礎編/応用編

- 関連製品:[VOD]Pythonで学ぶ マクスウェル方程式 【電場編】+【磁場編】

- 関連製品:[VOD]Pythonで学ぶ やりなおし数学塾1【微分・積分】

- 関連製品:[VOD]Pythonで学ぶ やりなおし数学塾2【フーリエ解析】

- 関連記事:5G時代の先進ミリ波ディジタル無線実験室 [Vol.8 初めての28GHzミリ波伝搬実験]

- 関連記事:超長距離無線LoRaからローカル5Gまで!GNU Radio×USRPで作るソフトウェア無線機

ご購入前の確認事項とお願い ~利用可能な周波数~

本製品は,内蔵のSTM32マイコンにジッタ・クリーナAD9545の出力周波数などを制御するファームウェアが書き込まれています(開発:ラジアン).利用できる周波数は次の5種類です.

- 1PPS

- 10MHz

- 30.72MHz

- 61.44MHz

- 122.88MHz

本製品は,100k~700MHzのクロック信号を生成する実力をもちますが,1PPS/10MHz/30.72MHz/61.44MHz/122.88MHz以外の周波数を生成したい場合は,ご自身でファームウェアを開発していただく必要があります.

周波数100k~700MHz,精度10$^{-10}$のウルトラ・プレシジョン・シンセサイザ

z-pptgenは,周波数精度の極めて高いルビジウムを搭載したGPS衛星の受信信号から得られる1kHzからジッタ成分を除去し,この信号を基準にPLLを使って安定性の高い高C/N信号を生成します.出力は,1PPS/10MHz/30.72MHz/61.22MHz/122.88MHzです.次世代無線規格 サブ6GHz 5Gや広帯域ディジタル無線の通信実験など,幅広い用途に利用できます.

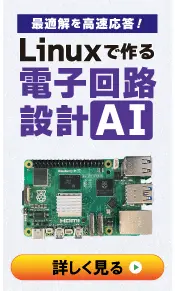

デュアル・ディジタルPLLによって独立した2系統のジッタ・クリーニングされた基準周波数を出力するAD9545(アナログ・デバイセズ)を搭載しています.AD9545は,同載のマイコンでコントロールしますから,本キットは,スタンドアロンで手軽に高精度クロックが得られます.

内容物

- 本体

-

GPSアンテナ:MIKROE-3373

メーカ名:MIKROE

周波数範囲:1595.42M±25MHz

インピーダンス:50Ω

VSWR:2:1以下

ゲイン:30dB

帯域:5MHz

雑音指数:1.5dB

電源電圧:3~5V

ケーブル長:3m -

ACアダプタ:AD-T50P200

メーカ名:XIAMEN UME ELECTRONICS

出力:5V,2A,10W

接続部:内径2.1mm,外径5.5mm,センタ・プラス

ケーブル長:1.5m - 解説動画と講義テキストの視聴/ダウンロードURLとパスワード

技術資料

紹介動画

| 動画1 pptGenのキー・デバイス 低ジッタ・クリーナ AD9545 | 動画2 ルビジウム発振器と同レベル!pptGenは10$^{-10}$の超高精度 | 動画3 pptGenの使い方 |

本キットを購入された方へ ~解説動画の視聴リンクとパスワード~

下記リンク先(青字)をクリックして,本製品購入後にメールにてお知らせしたパスワードを入力してください.

280分解説ビデオ(著作権保護のためパスワードがかけられています)

GPSクロック・ジッタ・クリーナpptGen解説動画.mp4

- 0:00:10 自己紹介

- 0:03:00 5G実験基地局で使用、GPSクロックジッタ・クリーナ

- 0:06:00 GPSから得られる高精度クロック

- 0:09:57 NEO-7M の UART から出力される情報

- 0:12:03 GPSから得られる高精度クロック

- 0:13:26 周波数精度とJitter($C/N$)

- 0:15:48 Time Pulse = 10MHz の波形

- 0:17:24 周波数が高くなるほど$C/N$は悪化する

- 0:19:13 ジッタ,$C/N$の悪化はどのような影響がある?

- 0:25:16 基本1:GPSモジュールで高精度クロックが得られる

- 0:26:25 PLLシンセサイザ REF の $C/N$ を見せる場合

- 0:35:48 PLLシンセサイザ VCO の $C/N$ を見せる場合

- 0:40:08 GPSから得られる高精度クロックのジッタを取り除く

- 0:41:44 データシートAD9545

- 0:43:29 AD9545から出力されるジッタ

- 0:50:11 基本2:狭帯域PLLでREFのジッタを除去できる

- 0:52:27 これまでのPLLシンセサイザ設計

- 0:59:41 AD9545評価ボードと評価ソフトウェア

- 1:01:37 AD9545の設定レジスタを調べる方法

- 1:04:41 AD9545のStatusを調べる方法

- 1:07:07 Systemクロックを設定

- 1:09:41 クロック出力を設定

- 1:11:23 DPLL Divider の設定

- 1:13:14 DPLL NCO の設定

- 1:15:51 DPLL Loop フィルタ周波数の設定

- 1:19:06 REF入力の設定

- 1:20:06 基本3:最近の専用チップは評価ソフトを使って設計

- 1:23:41 VCOの電源はローノイズでなくてはならない

- 1:31:09 Ultra Low Noize LDOのパターン図

- 1:35:01 基本4:VCOの電源は徹底的にLow Noise化する

- 1:42:22 実験:ルビジウム内蔵SGと比較して検証する

- 1:53:16 AD9545 GPS Timepulse Jitter Cleaner Board

- 2:04:38 伝送路の等価回路

- 2:12:09 同軸ケーブルの特性インピーダンス

- 2:16:06 ストリップラインの特性インピーダンス

- 2:20:18 マイクロストリップラインの特性インピーダンス

- 2:22:49 マイクロストリップは層間厚の製造バラツキに要注意

- 2:26:05 ストリップラインの層入替は不整合が起こりやすい

- 2:29:52 基本5:用途に応じてパターン伝送路を選択する

- 2:34:26 差動線路のメリット

- 2:40:57 差動線路をシングルで使用する場合の問題点

- 2:43:54 今回採用した差動ではない平行線路

- 2:46:41 差動線路のリターン電流

- 2:50:00 基本6:差動伝送路を選ぶと良い理由と注意点

- 2:55:59 マイクロストリップで定在波が発生したらアンテナになる

- 3:03:07 ベタGNDでも定在波発生に注意

- 3:10:13 基本7:基板表面の定在波発生はアンテナと同じx

- 3:13:06 誘電損失の計算方法

- 3:18:07 表皮効果の計算方法

- 3:23:43 表皮効果と誘電損失の計算結果

- 3:27:42 基本8:高周波では基板材料の選択に注意

- 3:30:45 差動線路を評価する場合の問題

- 3:38:27 ミックス・モード$S$パラメータの必要性

- 3:43:29 Mixed Mode S parameter (3port)算出方法

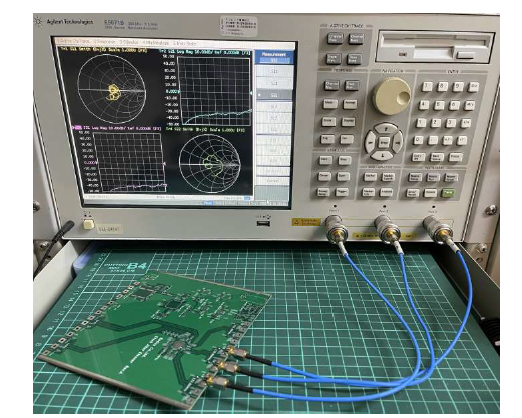

- 3:46:26 VNAにMixed Modeを設定する場合

- 3:48:46 VNAで3ポート$S$パラメータ測定

- 3:51:03 Qucs Studio でミックスモード解析

- 3:57:49 基本9:差動線路の評価には$S$パラ・ミックスモードが必須

- 3:58:56 GPS ANT経路マイクロストリップ 1.5GHz

- 4:02:44 Stub 1mmの影響を見積もる

- 4:08:41 Short Stub $λ$/4は存在が無視できる

- 4:11:39 SMA水平か垂直か

- 4:15:25 基本10:GHz帯は意図せぬスタブに注意

- 4:16:38 AD9545 GPS Clock ボードの操作方法

- 4:27:04 AD9545 GPS Clock ボードの同期実験

- 4:30:34 AD9545 GPS Clock 122.88MHz波形

- 4:33:43 GPSクロック基板の製作はマルツエレック・プロトファクトリが承ります