超高精度-10乗!GPSクロック・ジッタ・クリーナの設計

高$C/N$&低ジッタPLLシンセサイザの作り方(講義280分/82頁)

- 著者・講師:加藤 隆志/Takashi kato

- 企画編集・主催: ZEPエンジニアリング株式会社

- 1人当たり1ライセンスです

お申し込み

下記のボタンを押して,必要事項の入力をお願いいたします.

お申込み前にご理解いただきたいこと

- 本VODは,2022年8月20日に開催したウェビナを録画して編集した動画です.繰り 返し再生,一時停止,巻き戻しが可能です.

講義の内容

あらまし

ICやモジュールの完成度が上がった現代のハードウェアの信頼性や性能のかぎを握るのは「プリント基板の性能」です.多くのディジタル回路が数百Mbps以上で動作するようになり,アナログ・センスが欠かせない時代です.

プリント基板上では,電圧,電流,電磁界などのさまざまな物理量が複雑にふるまいますから,パフォーマンスの高い基板を設計できるのは,設計経験豊富な一部のアナログ技術者に限られています.

本セミナでは,GHz超の高速ディジタル回路や高周波アナログ回路の設計者が,無数の基板設計ノウハウの中から,特に重要な10個のポイントをシミュレーションや実験結果を交えて解説します.

解説にあたっては,GPS受信信号から得られた超高安定クロックを使って極めて周波数精度の高いクロックを生成すると同時に,その信号を使って広帯数百MHzにも対応できるディジタル変調用の高C/Nクロックが得られる基準クロック源を例とします.デュアル・デジタルPLLによって独立した2系統のジッタ・クリーニングされた基準周波数を出力するAD9545(アナログ・デバイセズ)を搭載しています.AD9545は,SPIまたは$I^{2}C$でコントロールしますが,製作する基板にはマイコンを内蔵しスタンドアロンで手軽に高精度クロックが得られるボードを目指します.

|

|

|---|---|

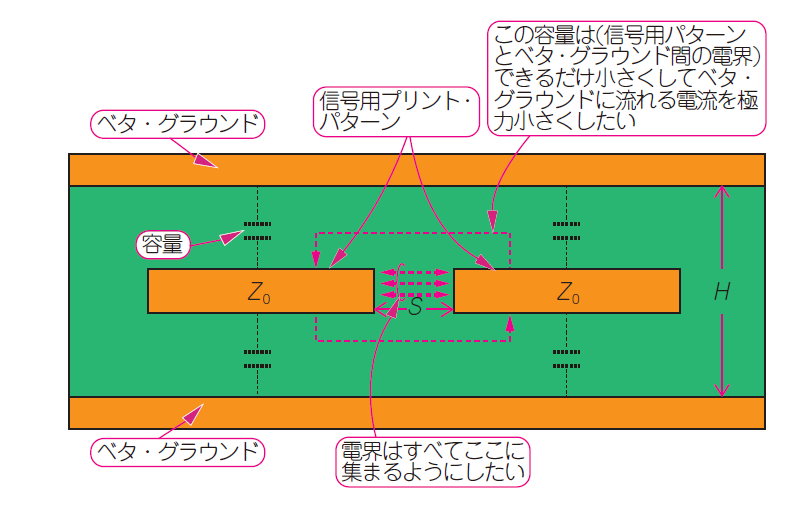

| 図1 差動線路はリターン電流の専用経路が確保されているため,信号用プリント・パターンの下層にあるベタ・グラウンドのスリットによってリターン電流の経路が経たれるような問題は発生しない | 図2 最もよく使われている内層配線型のストリップ差動線路 |

演目

(1)つなぐだけ基板設計の問題点

- 電源の問題点

- 高速ディジタル伝送の問題点

- 広帯域アナログ信号伝送の問題点

ほか

(2)電源編

- [ポイント1]パスコンの実装

- [ポイント2]ベタ・パターンの必要性

- [ポイント3]電源回路の応答性

(3)伝送線路編

- [ポイント4]インピーダンス・マッチング

- [ポイント5]クロストーク

- [ポイント6]リターンのケア

(4)クロック回路編

- ジッタの基礎

- シンセサイザの基礎

- ループ・フィルタの基礎

- 基準発振源の基礎

受講対象

- 本セミナの例題「GPS高精度基準クロック基板」

- 高速ディジタル基板の設計者

- 計測用アナログ回路基板設計者

- 広帯域な無線通信用の高周波基板設計者

講師紹介

略歴

- 1990年 無線通信機器メーカで設計開発.その後,計測器メーカでRF測定機器,半導体試験装置の設計開発

- 2017年 フリーランスエンジニアとして独立,無線通信機器やSDR機器の受託開発

- 2019年 株式会社ラジアンとして法人化,現在に至る

主な著書

- 電波解読マシン Piラジオの製作,トランジスタ技術,2017年1月号 特集,CQ出版社.

- 電波超解像!スペクトラムプロセッサSDR誕生,トランジスタ技術,2018年9月号 特集,CQ出版社.

- 夢のRFコンピュータ・トランシーバ製作,トランジスタ技術,2017年8月号 連載,CQ出版社.

- 信号処理プログラミングで操るソフトウェア無線機&計測機,2019年春号,トランジスタ技術SPECIAL No.146,CQ出版社.