1度は必ず見舞われる定番トラブル「発振」と対策

実験キットで学ぶ初歩電子回路設計

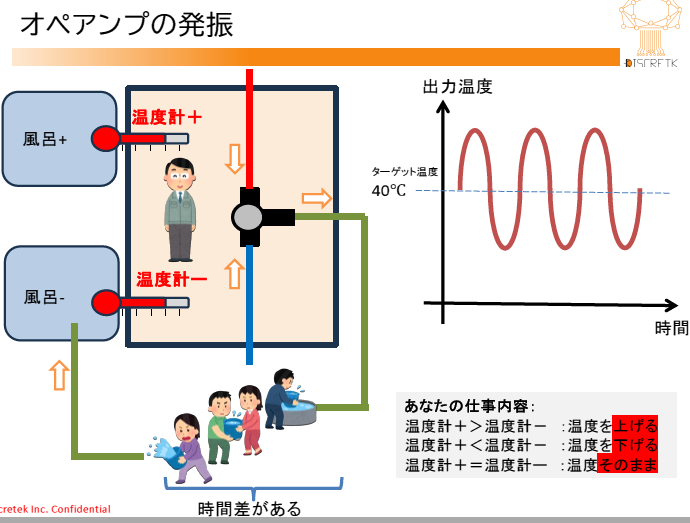

発振が起こる原因

|

|---|

|

図1 発振は位相補償を適切に施すことで安全に制御できる.回路の寄生素子や信号遅延を理解し,小容量のキャパシタを追加することで対策できる.画像クリックで動画を見る.または記事を読む.[講師]善養寺薫(ディスクリテック) 詳細:[VOD/KIT/data]実験キットで学ぶ初歩の電子回路設計 |

電子回路では,出力側に余計な要素がある場合や回路間に隠れた寄生素子が存在する場合,発振が起こります.基板上で目に見えないキャパシタやインダクタが形成されることもあります.これにより信号が遅延し,出力電圧が安定する前にバタバタと変動する現象が発生します.

OPアンプの内部動作を理解する上で重要なのは,理論式だけでは捉えにくい現象が現実には存在することです.0.1μFのキャパシタが信号経路に入ることで,充電が完了するまで電圧が追従せず,発振の原因となることがあります.

位相補償による発振対策

発振を防ぐ方法として位相補償回路があります.OPアンプの出力と負入力の間に小さなキャパシタを挿入することで,OPアンプの応答速度を遅くして安定化させます.この方法により出力のバタバタした揺れを抑えることが可能です.

位相補償は設計段階でシミュレーションや計算で確認されます.実際のプリント基板設計では,まず試作品を作成し,必要な箇所にキャパシタを挿入して最適な値を探す手法がよく用いられます.ただし,過剰に大きい値を入れると応答が遅くなり,出力波形に遅れが生じます.

実験キットで確認すべきポイント

発振の確認として,出力が安定せずバタバタ変動する現象が起きるかを確認します.

位相補償キャパシタの効果として,小さなキャパシタを挿入して出力が安定するかを観察します.

過剰挿入の影響として,キャパシタを大きくすると出力応答に遅れが出るかを確認します.

回路全体のバランスとして,設置したキャパシタがほかの回路動作に影響していないかを確認します.

回路設計上の注意点

発振は避けられない場面もありますが,位相補償を適切に設計することで安全に制御できます.回路の寄生素子や信号遅延を理解し,必要に応じて小容量のキャパシタを挿入することが重要です.

実験キットを用いて実際に発振を観察し,位相補償の効果を体感することが,初歩電子回路設計における理解を深める近道です.OPアンプの特性を考慮した設計を行うことで,現実の回路でも安定した出力が得られます.

〈著:ZEPマガジン〉参考文献

- [VOD]高速&エラーレス!5G×EV時代のプリント基板&回路設計 100の要点,ZEPエンジニアリング株式会社.

- [VOD] Before After! ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

- [Book/PDF]デシベルから始めるプリント基板EMC 即答200,ZEPエンジニアリング株式会社.

- [VOD/KIT]ポケット・スペアナで手軽に!基板と回路のEMCノイズ対策 10の定石,ZEPエンジニアリング株式会社.

- [VOD]事例に学ぶ放熱基板パターン設計 成功への要点,ZEPエンジニアリング株式会社.