新人技術者のためのRISC-V CPU設計 初めの一歩

C言語完全対応!HDLソース 500行のミニCPUを一緒に作る(講義723分/解説402頁)

- 著者・講師:圓山 宗智

- 企画編集・主催: ZEPエンジニアリング株式会社

- 関連製品:[VOD/KIT]実習キットで一緒に作る!オープンソースCPU RISC-V入門

- 関連製品:[VOD]ARM/GPU/FPGA/RISC-Vで作る AIカメラ&IoTエッジ開発 100の要点

- 関連製品:[VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】

- 関連製品:[VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門

お申し込み

下記スケジュール表のボタンをクリックし,必要事項の入力をお願いいたします.

| 内容 | キット |

テキスト& 実習ソース |

視聴期間 | 税込価格 | 申し込み |

|---|---|---|---|---|---|

|

[録画] 新人技術者のためのRISC-V CPU設計 初めの一歩 |

× | × | 2日 | 50,000円 | |

|

[VOD/KIT/data] 新人技術者のためのRISC-V CPU設計 初めの一歩 |

〇 | 〇 | 無制限 | 88,000円 | |

|

[VOD/data] 新人技術者のためのRISC-V CPU設計 初めの一歩 |

× | 〇 | 無制限 | 60,500円 |

ご購入前にご理解いただきたいこと

- 本VODは,2025年5月31日,6月1日に実施したセミナを録画して編集した動画です.繰り返し再生,一時停止,巻き戻しが可能です.

- すべての映像,画像,文書テキスト,ソースコードは,著作権法によって厳格に守られています.無許可の転載,複製,転用は法律により罰せられます.

実習キットの構成

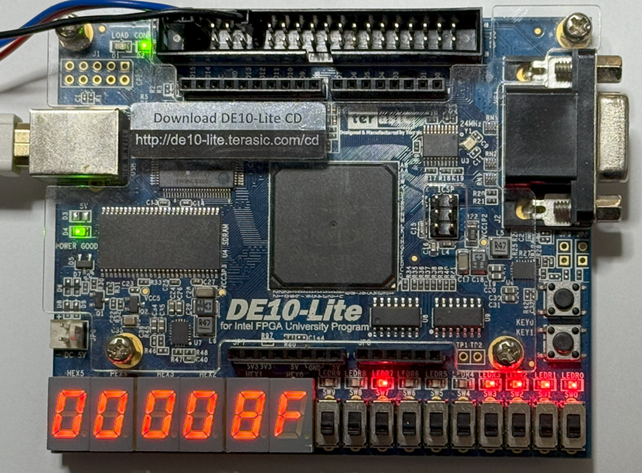

- Terasic DE10-Liteボード(FPGA:MAX10M50DAF484C7G,64MB SDRAM, 3D加速度センサ,USBケーブル付属)

- メス-メス・ジャンパ(15cm,6本)

- FT234X 超小型USBシリアル変換モジュール

- USBケーブル(TypeA - MicroB):PCとUSB-UART変換基板の接続用

- ピンヘッダL型1x3

※本セミナで使用するハードウェアの一覧はこちらをご参照ください.

学ぶこと

本セミナでは,コンピュータの基本構成からはじめて,オープンな命令セットを持つRISC-V CPUの登場の意味と,その最も基本的な命令セットRV32Iを学びます. RISC-Vのソフトウェア開発環境を立ち上げ,アセンブラまたはC言語によるプログラムの作成方法を習得します.

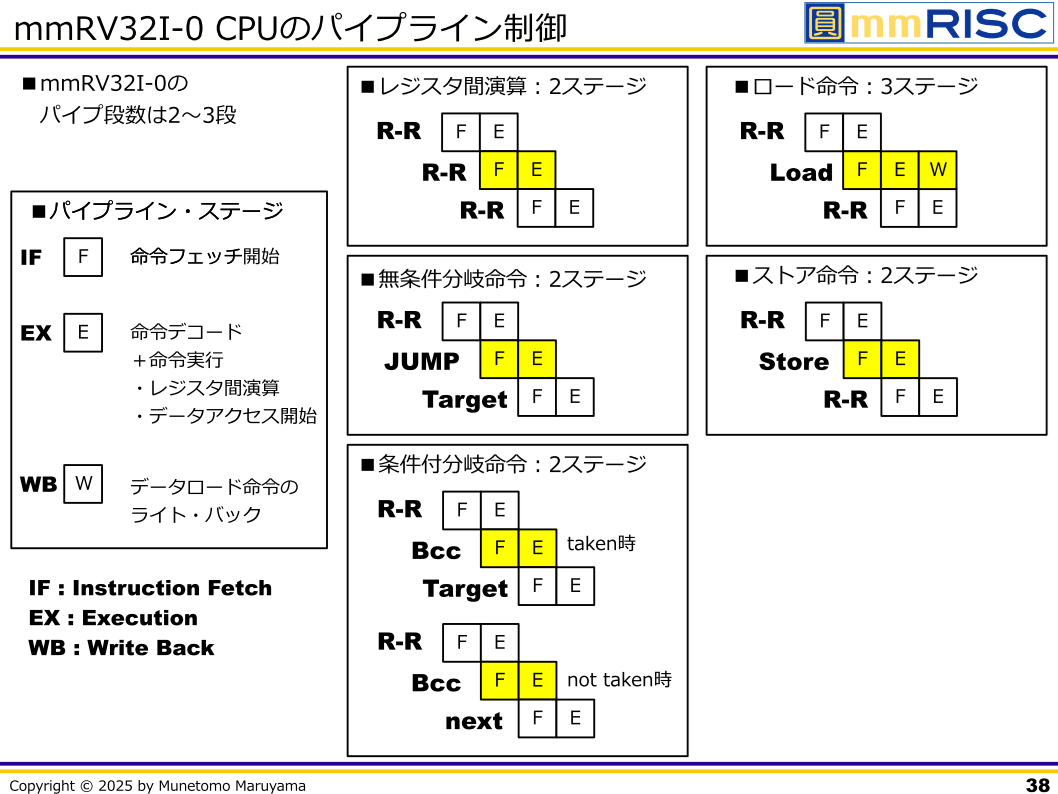

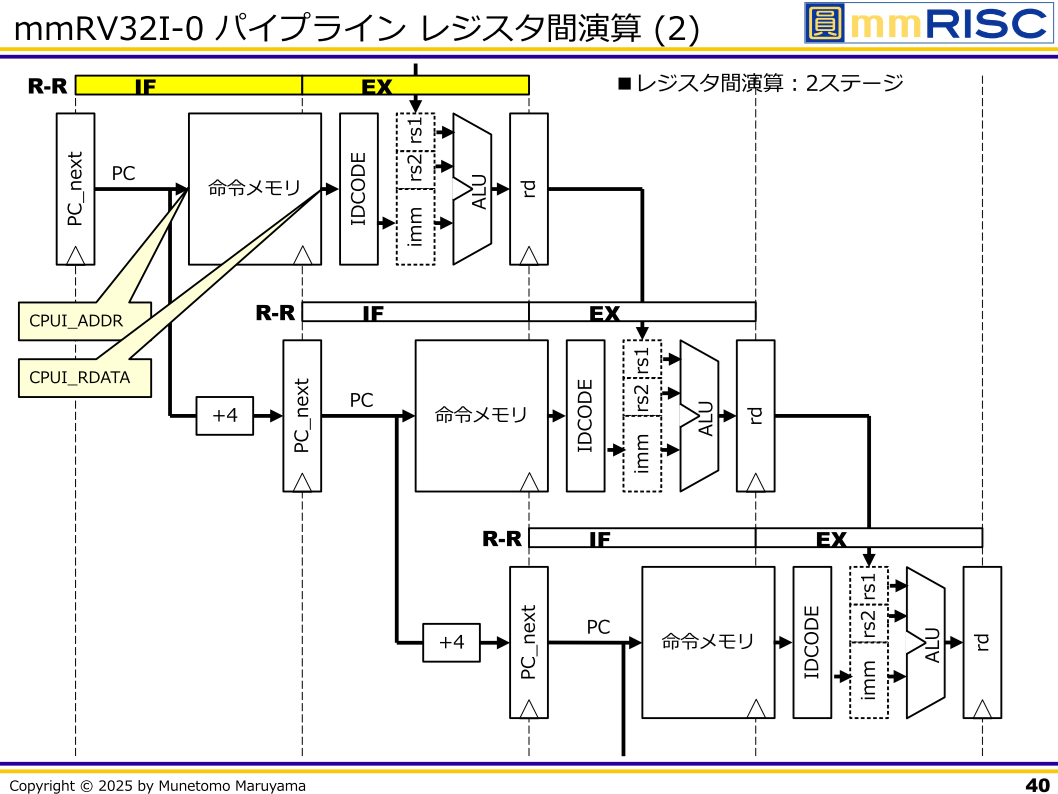

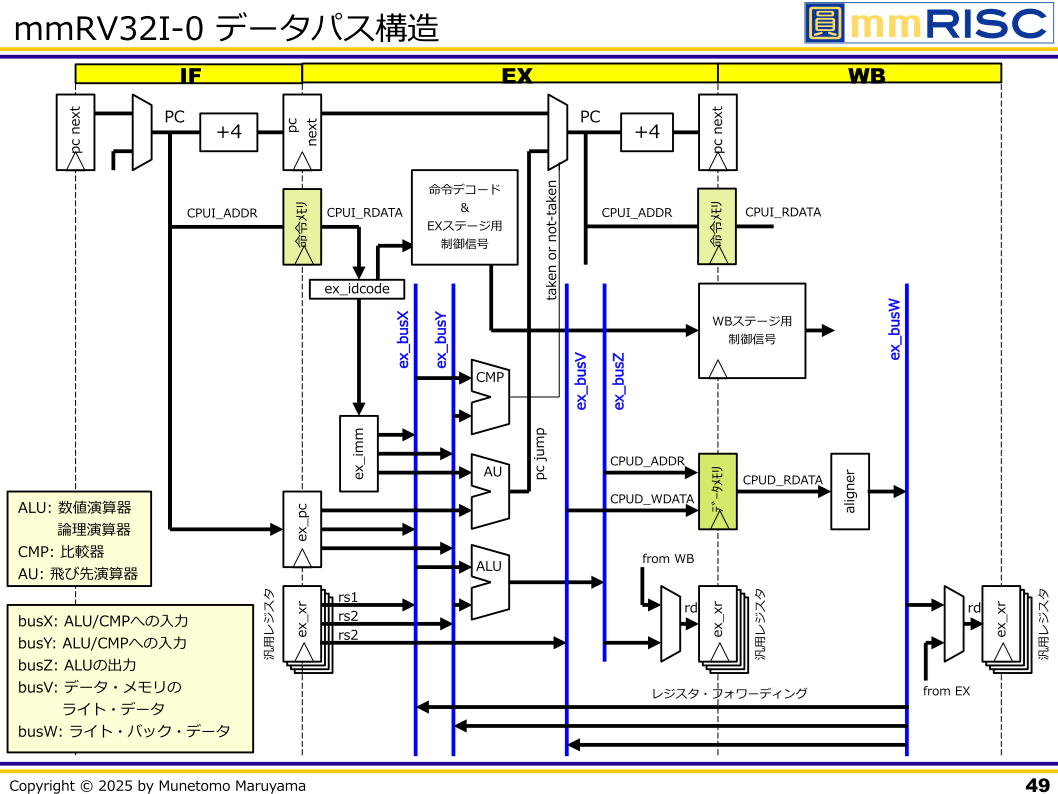

RV32I基本命令を持つCPUの内部アーキテクチャを,シンプルな2~4段パイプライン構成として検討し,その論理設計手法を学びます. 実際に,そのCPUを500行程度のSystemVerilogで記述し,メモリと周辺機能と合わせて一つのコンピュータ・システムとして論理シミュレーションで動作確認します.

最終的にそのシステムをFPAGに実装して,C言語でいろいろなプログラムを作成して動作させてみましょう.

本セミナを通して、RISC-Vコンピュータ・システムのハードウェアからソフトウェアまでの全般を具体的に理解することができます.

アジェンダ

1日目

(0) 開発環境のインストール

- FPGA設計環境 Quartus Prime

- 論理シミュレータ Questa Simとライセンス取得

- ソフト開発環境 Eclipse IDE

- 設計データ

(1) マイコンの基礎

- 本質的にコンピュータがやること / CPU+バス+メモリ / 周辺機能 / コンピュータ・システム

(2) RISC-Vの登場

- RISC-Vのインパクト / RISC-V CPUコアを自作する意味

(3) RISC-Vの命令セット

- RISC-Vの命令体系とその拡張性 / RV32I命令の詳細

(4) RISC-Vのソフトウェア開発環境

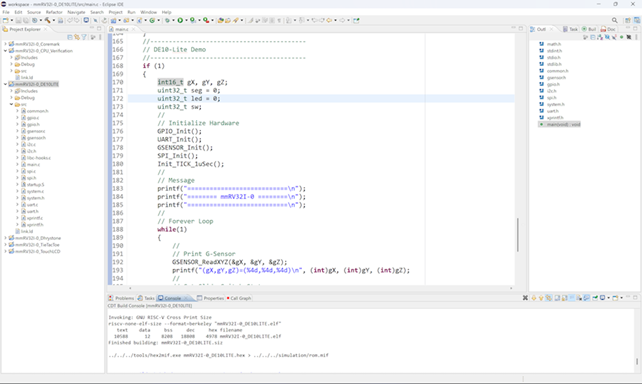

- 環境立ち上げ / 簡単なCプログラムのビルド / Cプログラムの構造とリンク

- アセンブル・プログラムのビルド / 逆アセンブルによる生成コードの確認方法

(5) メモリとバス

- メモリ信号とタイミング / バス信号とタイミング / マルチレイヤ・バス

- FPGAのメモリとデータ内容の初期化方法

(6) CPUの仕様と内部アーキテクチャ

- CPUの仕様

- 命令フェッチ / 命令デコードと実行 / メモリ・アクセス / ライトバック

- パイプライン動作 / 内部構造と動作タイミング / 命令前後の影響とフォワーディング

2日目

(7) CPUのSystemVerilog記述

- 500行を追いかける

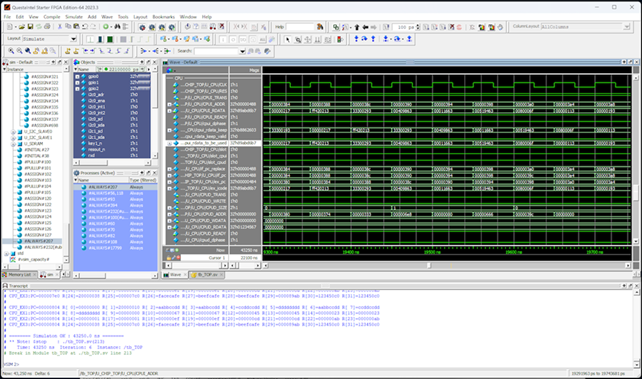

(8) CPUの論理シミュレーション

- チップ・トップの記述 / テストベンチ記述

- 検証プログラム / 論理シミュレーションの実行方法 / 結果の確認

(9) 周辺機能

- 周辺機能を含むコンピュータ・システムの構成

- 外部I/O PORTの機能仕様と論理シミュレーション

- UARTの機能仕様と論理シミュレーション

- SPIの機能仕様と論理シミュレーション

- I2Cの機能仕様と論理シミュレーション

(10) コンピュータ・システムのFPGAへの実装

- Quartus Primeの設定

- Quartus PrimeによるFPGAの合成とコンフィギュレーション

(11) 各種CプログラムをFPGAボードで動かす

- LED点滅

- UART通信とprintf()

- FPGAボード上の3軸加速度センサの読み取り

- TicTacToeゲーム

- ベンチマーク Dhrystone

- ベンチマーク Coremark

- (LCDタッチパネルを使った応用例)

(12) さらに本格的なCPUを目指すには

- 例外処理と割込み

- オンチップ・デバッガ

キーワード解説(著:ZEPエンジニアリング)

RISC-V(Reduced Instruction Set Computing - Version 5)

オープンソースの命令セット・アーキテクチャ(ISA).シンプルかつ拡張性の高い設計を特徴とする.従来の商用ISAとは異なり,特許やライセンス料が不要であるため,企業や研究機関が自由にカスタマイズできる.RISC(Reduced Instruction Set Computer)を基盤とし,効率的な命令セットを採用することで,省電力かつ高性能なプロセッサを開発できる.自作CPUを個人ではなく,多くの人と共有できる最新環境である.

DE10-Lite

Altera社のMAX 10 FPGAを基盤とした開発ボード.最大50Kのロジック要素と内蔵A-Dコンバータを備え,USB-Blaster,SDRAM,加速度センサ,VGA出力,2x20 GPIO拡張コネクタ,Arduino UNO R3拡張コネクタなどを備える.産業用や自動車,消費者向け市場向けにシステム・レベルのプロトタイピングに適しており,多くの参照設計データやソフトウェアが提供されている.

・参考ページ:DE10-Lite Board

命令セット

コンピュータのプロセッサが理解し実行するための命令の集合.これらの命令は,プロセッサの機能や動作を制御するために使用される.命令セットは,データの演算や処理,入出力の管理,メモリの操作などを行うために必要な基本的な命令を定義しており,コンピュータのアーキテクチャにおける基盤となる.RISCやCISCといった命令セットの設計方式が存在し,その実体はハードウェア(回路)である.

SystemVerilog

ハードウェア設計と検証のために使用されるハードウェア記述言語(HDL)で,Verilogを拡張したものである.シミュレーション,検証,合成のための強力な機能を提供し,テストベンチの作成や機能検証を容易にする.オブジェクト指向プログラミングの概念やコンストレイント・ベースの検証手法などを取り入れ,複雑なデジタル回路の設計効率を向上させる.

論理シミュレーション

デジタル回路設計の動作をモデル化し,設計が期待通りに機能するかを検証するためのプロセス.回路の動作をシミュレーションすることで,実際のハードウェアを作成する前に問題を特定し修正でき,コストを削減できる.

受講対象

- コンピュータ・システムとCPUの内部構成の基礎を学びたい方

- コンピュータ・システムとCPUをFPGAに実装してCプログラムで動作させたい方

講演の目標

- RISC-Vをコアにしたコンピュータ・システムを独自に開発することができる

- セミナで教材に使ったシステムのメモリや周辺機能の拡張ができるようになる

- RISC-Vのさまざまなアプリケーション・プログラムの開発を通して,ハードウェアとソフトウェアを統合したシステム全体の開発能力を取得する

あると望ましい予備知識

- 論理回路の基礎知識

- Verilog記述とSystem Verilog記述の基礎知識

- C言語の基礎知識

受講者が事前に準備するもの

- パソコン:64ビットWindows 11,空きディスク30GB以上,メモリ8GB以上

- 事前インストール(セミナ開催前にお知らせする方法で事前にインストールすること)

講師紹介

略歴

- 出身地 :京都市左京区

- 趣味 :1978年からマイコン・FPGAを趣味として,論理設計やプログラム開発を楽しむ

- 仕事 :1986年からマイコンLSI・半導体デバイスの設計に従事

- 執筆活動:2000年からマイコンを絡めた雑誌記事と書籍を執筆

主な著書

雑誌記事 約100本程度執筆

- ARMベース・システムLSI開発の事例研究,Design Wave Magazine 2006年5月号,CQ出版社.

- ARM汎用プロセッサで使える汎用JTAGデバッガを自作する,Design Wave Magazine 2008年6月号,CQ出版社.

- 並列処理プロセッサxCORE徹底研究,インターフェース 2014年11月号~2015年6月号(連載),CQ出版社.

- Cで直叩き!超並列コンピュータGPU全速力,トランジスタ技術 2019年9月号(特集),CQ出版社. ほか

書籍

- 今すぐ使えるH8マイコン基板 初版2010年,増補版2011年,CQ出版社.

- 2枚入り小型ARMマイコン基板 2011年,CQ出版社.

- ARM PSoCで作るMyスペシャル・マイコン 基板付き 2013年,CQ出版社.

- ARM PSoCで作るMyスペシャル・マイコン 開発編 2013年,CQ出版社.

- SHマイコン活用記事全集 2014年,CQ出版社.

- FPGA電子工作スーパキット 2016年,CQ出版社.

- MAX10実験キットで学ぶFPGA&コンピュータ 2016年,CQ出版社.

- 完全版FPGA電子工作オールインワン・キット 2016年,CQ出版社.

講演の参考文献

- デイビッド・パターソン他,RISC-V原典 オープンアーキテクチャのススメ, 2018, 日経BP

- The RISC-V Instruction Set Manual Volume I: Unprivileged Architecture Version 20240411

- TDE10-Lite User Manual v1.6, Oct.2018, Terasic Inc.

- Questa SIM Command Reference Manual, Software Version 2023.3, Document Revision 8.3, Siemens