|

|---|

Zynq搭載ボードの決定版“Eclypse Z7”で始める

高速信号処理システム開発

~100Msps ADC/DACで作る測定器/データ・ロガー/LinuxベースSDR~

[Vol.1 開発環境“Vivado”をインストールしてFPGA(PL)でLチカ]

- 著者・講師:別府 伸耕/Nobuyasu Beppu (リニア・テック)

- 企画編集・主催: ZEPエンジニアリング株式会社

- 関連製品:[VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門

- 関連製品:[VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門

- 関連製品:[VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門

- 関連製品:[VOD]Pythonで学ぶ やりなおし数学塾1【微分・積分】

- 関連製品:[VOD]Pythonで学ぶ やりなおし数学塾2【フーリエ解析】

- 関連製品:[VOD]Pythonで学ぶ マクスウェル方程式 【電場編】+【磁場編】

- 関連製品:[VOD/KIT]初めてのソフトウェア無線&信号処理プログラミング 基礎編/応用編

- 関連記事:超長距離無線LoRaからローカル5Gまで!GNU Radio×USRPで作るソフトウェア無線機

- 関連記事:高精度基準搭載&1GSPS広帯域! プロ用USBマルチ測定器 ADP5250誕生

- 関連記事:Pythonではじめる 数値解析入門 [Vol.1 Pythonの開発環境をインストールする]

- 関連記事:Pythonではじめる 数値解析入門 [Vol.2 グラフ描画ライブラリ“Matplotlib”で2次元のグラフを描く]

【Index】

Vol.1 開発環境“Vivado”をインストールしてFPGA(PL)でLチカ

Vol.2 C言語プログラムでZynqの“PS”を動かす実験

Vol.3 PLによるディジタル・フィルタのサンプル・プロジェクトによる実験

“Eclypse Z7”ボードで高速信号処理システムを作ろう!

FPGAとCPUの複合デバイス“Zynq”を使いこなす

本連載では,Xilinx(ザイリンクス)社のデバイスである“Zynq”(ジンク)を活用したディジタル信号処理システムの構築方法を基礎知識から解説していきます.一連の実験はDigilent(ディジレント)社製の“Eclypse Z7”(エクリプス・ゼット・セブン)ボード(写真1)を使って行います.なお,本連載で解説するZynqの開発フローは他のZynq搭載ボードに対しても適用できるので,ご自身の環境にあわせて適宜読み替えてください.

連載の第1回ではEclypse Z7ボードの紹介と,無償で利用できる開発環境“Vivado”(ビバド)のインストール方法を解説します.また,Zynq内部のFPGAにLED点滅回路(いわゆるLチカ)を作る実験も行います.

なお,Eclypse Z7の詳しい情報は, こちらのWebページ から入手できます.

Zynqの基本構造

Zynqシリーズには回路規模が異なる様々なデバイスがありますが,基本的な構造は図1のようになっています.Zynqの最大の特徴は,1つのチップにFPGA(Field Programmable Gate Array)とCPU(Central Processing Unit)の両方が集積されていることです.FPGA部分は“Programmable Logic”,略して“PL”と呼ばれています.CPU部分は“Processing System”,略して“PS”といいます.

“PL”と“PS”の間は,“AXI”(Advanced eXtensible Interface)という規格のバスで接続されています.もともと,チップ内の回路ブロックどうしを接続するデータ・バスの規格として“AMBA”(Advanced Microcontroller Bus Architecture)というものが考案されました.AXIはチップ内の高速データ転送を目的として,AMBAの一部として作られた規格です.

Xilinx社から提供されているZynqの開発環境を使えば,PSやPLおよびAXIバスの開発を一貫して行うことができます.

Zynqを使えばオリジナル信号処理SoCを自由自在に作れる

Zynqの“PL”の部分は最先端のプロセスによって作られたFPGAであり,所望の演算処理を実行するために最適なハードウェアを作り込むことができます.また“PS”の部分には高性能なARMプロセッサが実装されていて,LinuxなどのOSを実行するプラットフォームとして十分な性能を持っています.さらにPSの部分にはUARTやSPI,$\mathrm{I^{2}C}$といった周辺回路(ペリフェラル)が豊富に含まれているので,外部回路とのやりとりも簡単に行えます.

PLによる高速信号処理をPSで実行するソフトウェアで柔軟にコントロールすることで,要求仕様に合わせたオリジナルな信号処理システムを作ることができます.ぜひZynqを使いこなして,自分だけの“SoC”(System on Chip)を作ってみてください.

“Eclypse Z7”ボードでZynqによる信号処理を手軽に体験

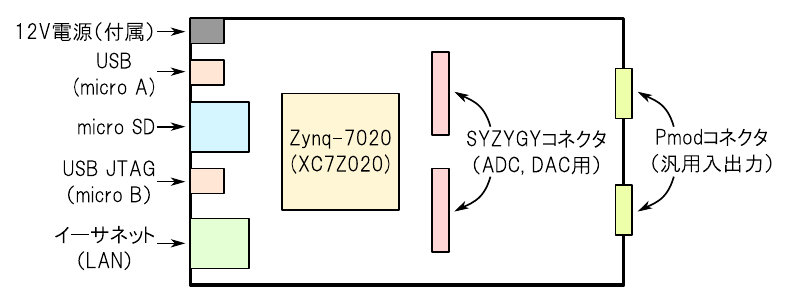

本連載では,Zynqを搭載したプロトタイピング・ボードである“Eclypse Z7”ボードを使って実験を進めていきます(写真1).このボードにはZynq用の電源回路やDDR3Lメモリ,micro SDのスロット,イーサネット用のコネクタなど,実際の運用に必要となるほとんど全ての部品が実装されています(図2).そのため,ハードウェア的には箱から出した状態のままですぐに実験を始めることができます.

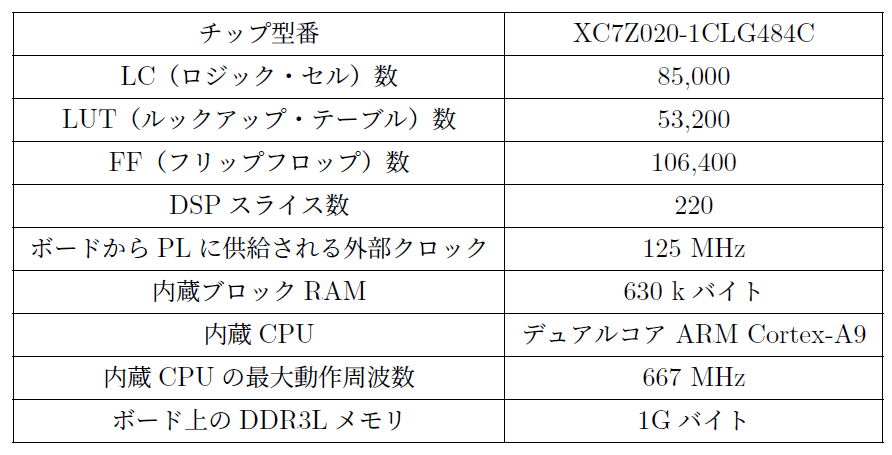

Eclypse Z7ボードに搭載されているのは,“Zynq-7020”(通称)というデバイスです.正式な型番は“XC7Z020-1CLG484C”です.このデバイスの仕様を表1に示します.ちょっとした実験をしたり小規模なシステムの試作をするには十分な性能をもっています.

“Eclypse Z7”ボードと100 Mspsの高速ADC/DACを組み合わせる

“Eclypse Z7”ボードは,“SYZYGY”規格に対応したコネクタを持っています(あえて日本語で読み方を書くなら「スィズィジィ・コネクタ」).“SYZYGY”は高速信号の伝送を目的としたロー・コストなコネクタの規格で,Eclypse Z7は“SYZYGY Standard”型のコネクタを2個持っています.

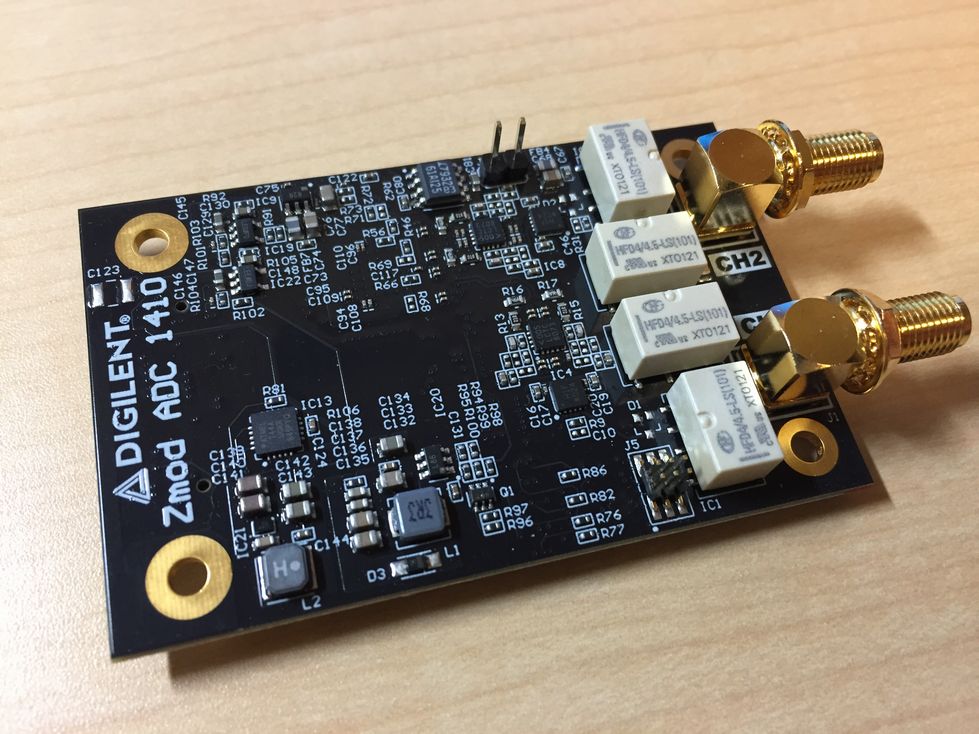

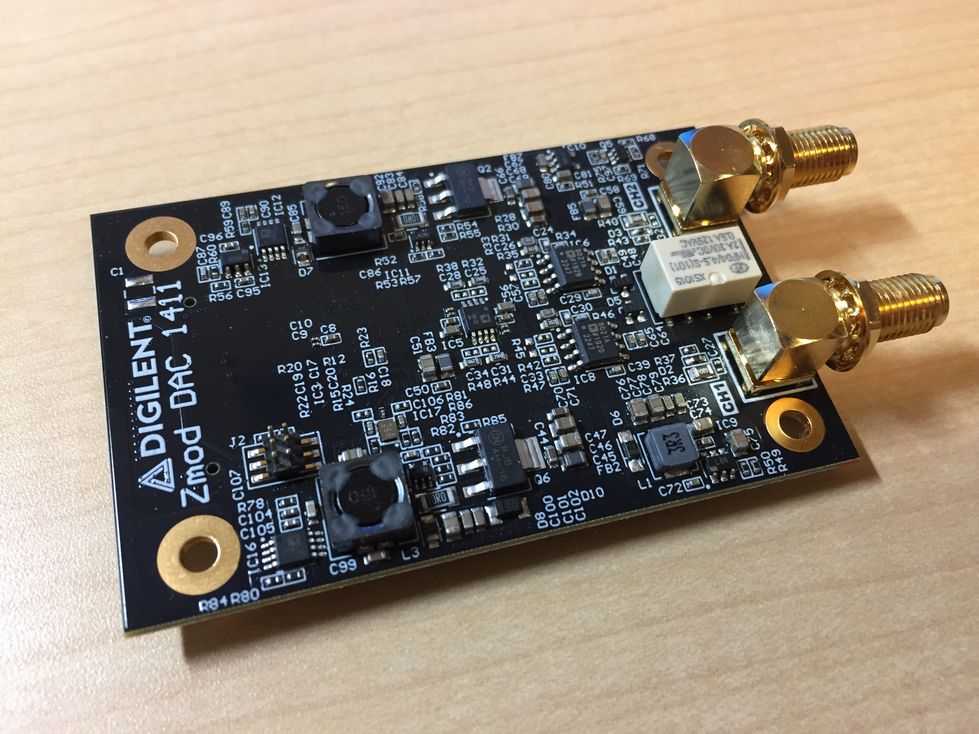

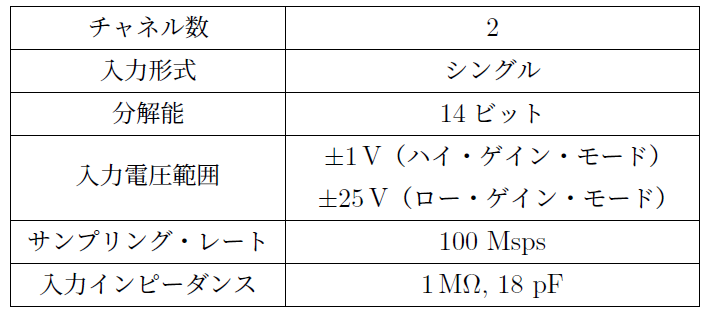

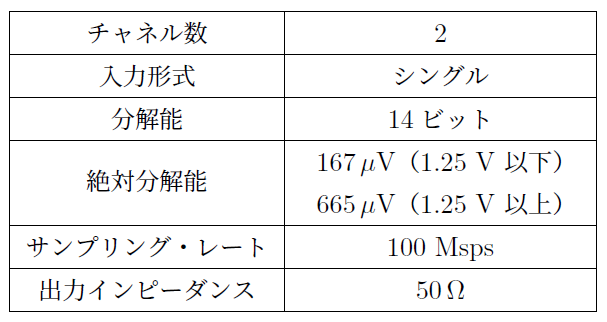

Digilent社は,SYZYGYコネクタで接続できる100 Mspsの高速AD変換(ADC)ボードおよび高速DA変換(DAC)ボードを発売しています.ADCボードの型番は“Zmod ADC 1410”(写真2)で,DACボードの型番は“Zmod DAC 1411”(写真3)です.これらのボードの仕様を表2および表3に示します.

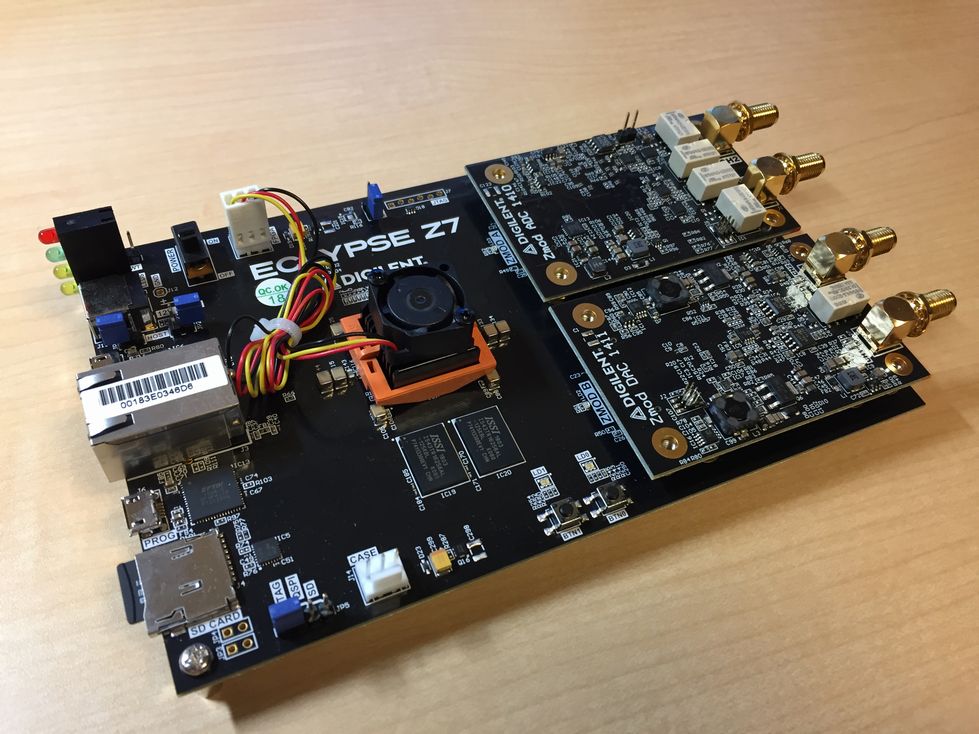

“Eclypse Z7”ボードに“Zmod ADC 1410”ボートと“Zmod DAC 1411”ボードを取り付けると,写真4のようになります.Eclypse Z7ボード上で“Zmod ADC 1410”や“Zmod DAC 1411”を活用するための設計例がDigilent社から提供されています.この情報は,オリジナルな信号処理システムを作る上で大いに参考になります.

Eclypse Z7ボードはZynqによる信号処理システムのお手本

写真4の「Zynq + 高速ADC + 高速DAC」というシステムを活用すれば,“SDR”(Software Defined Radio)を意識したディジタル変復調システムを手軽に構築することができます.他にも高速データ・ロガーやオリジナル測定器など,応用範囲は多岐に渡ります.Zynqは一種の「リコンフィギャラブル・デバイス」なので,万が一システム設計にミスがあったとしても迅速かつロー・コストで対応することができます.

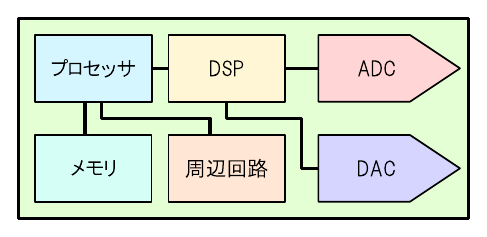

もともと,アナログ入出力を備える信号処理システムを構築するためにはADCやDACに加えて「プロセッサ」,「DSP」,「メモリ」,「その他の周辺回路」など多くの部品を基板上に並べる必要がありました(図3(a)).

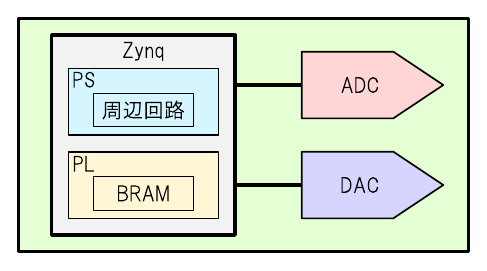

これに対して,ZynqはFPGA(PL)とCPU(PS)に加えて多くの周辺回路を内蔵しており,1チップでSoCとして機能します.そこにアナログ・フロント・エンドとして要求仕様に合わせたADCとDACを追加すれば,これだけで立派な信号処理システムが完成します.Eclypse Z7ボードはまさにこの構成になっており,Zynqを利用した信号処理システムの1つのお手本であると言えます(図3(b)).本連載では,Eclypse Z7ボードを使いこなして自由自在に信号処理システムを構築することを目指します.

|

|

|---|---|

| (a)従来の信号処理システムには多くのコンポーネントが必要だった | (b)Eclypse Z7ボード + Zmod ADC/DACによるシステム構成 |

| 図3 Zynqを利用すれば信号処理システムを簡潔にまとめられる | |

Zynqの開発環境“Vivado”をインストールする

開発に使うPCを用意する

Zynqを開発するときは,Xilinx社から提供されている開発環境の“Vivado”(ビバド)を利用します.回路規模が大きいチップを開発する場合は有料のライセンスが必要となりますが,Eclypse Z7ボードに載っているZynq-7020デバイスは無料で開発することができます.

ここから先の説明では,Windows10の64ビット版のOSを使うものとします.メモリ(RAM)は最低でも8G バイトは確保しておきたいところです.ハードディスクの容量は,Vivadoのインストールで46 Gバイトほど使います(今回の設定の場合).また,後でZynq用のLinux開発環境である“PetaLinux”(ペタリナックス)をインストールすることも考えると,合計100 Gバイト程度の空き容量が必要となります.余計なトラブルを避けて開発効率を上げるために,十分な性能の開発用PCを用意しておくことをお勧めします.

Vivadoのインストーラをダウンロードする

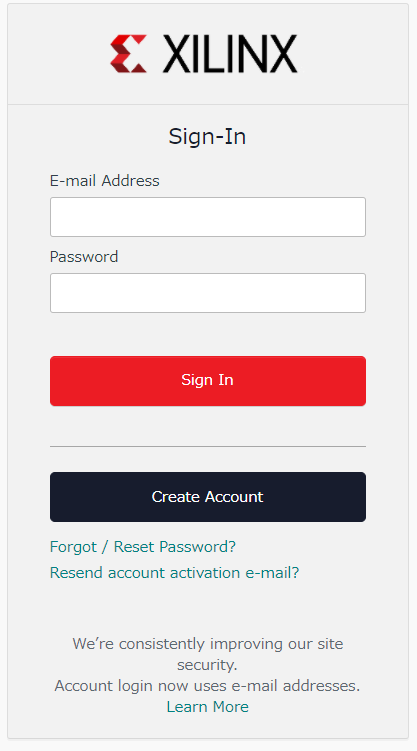

Vivadoのインストーラをダウンロードするために,Xilinx社のダウンロード・ページにアクセスします.アカウントは無料で作れるので,この機会に取得しておくことをおすすめします(図4).アカウントを取得したら,ログインします(図5).

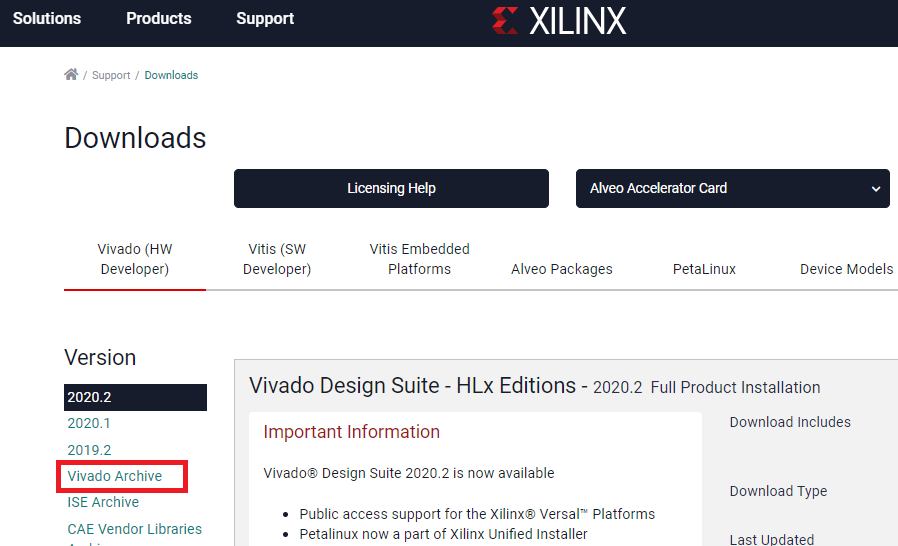

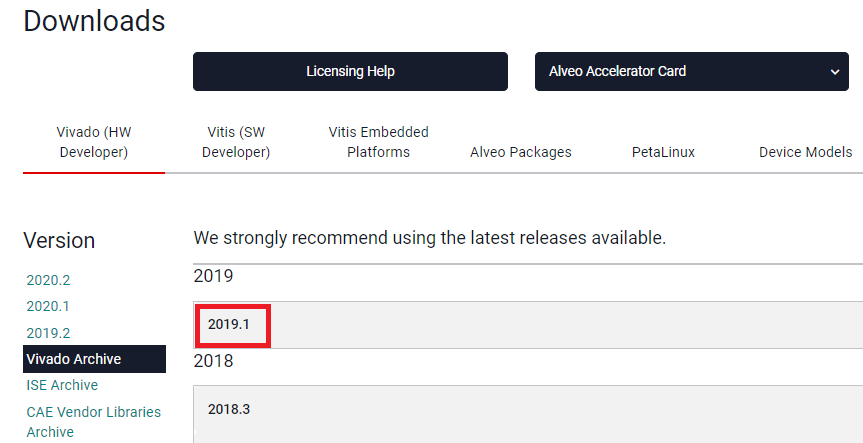

Vivadoにはリリース時期によって多くのバージョンが存在します.Eclypse Z7ボードを開発する際は,“Vivado 2019.1”を使うことが推奨されています.“Version”の欄から“Vivado Archive”をクリックして過去のバージョン一覧を開き(図6),“2019.1”をクリックします(図7).

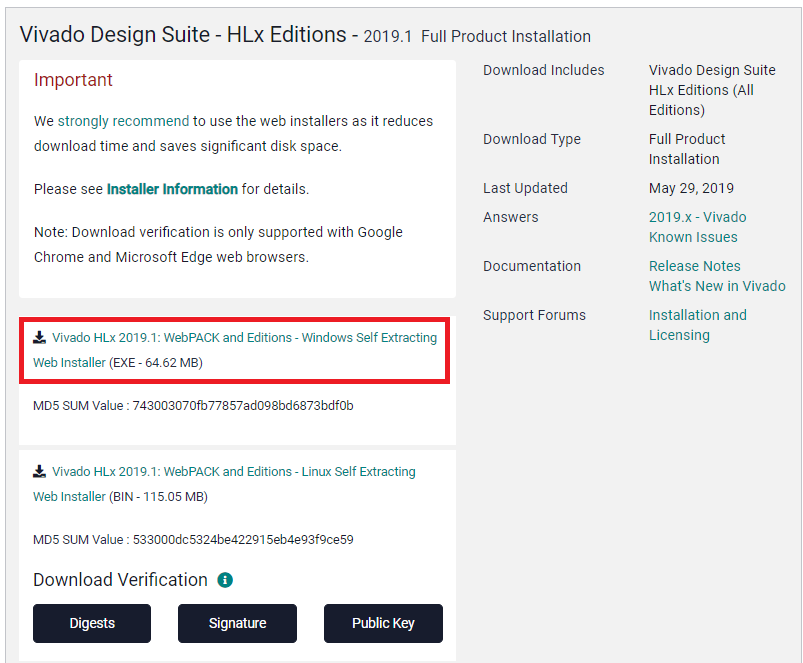

一覧の中から,Windows版の自己展開型インストーラである“Vivado HLx 2019.1: WebPACK and Editions - Windows Self Extracting Web Installer”を探してダウンロードします(図8).ダウンロード先は,デスクトップなどのわかりやすい場所にすることをおすすめします.

Vivadoをインストールする

ダウンロードしたインストーラをダブル・クリックして起動します(図9).インストーラを起動すると「このアプリがデバイスに変更を加えることを許可しますか?」というメッセージが出るので,「はい」をクリックします.

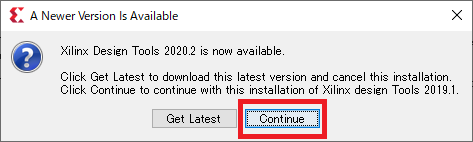

続いて最新のバージョンがあることを通知するウィンドウが出ますが,今回インストールするバージョンは“2019.1”で良いので[Continue]をクリックします(図10).

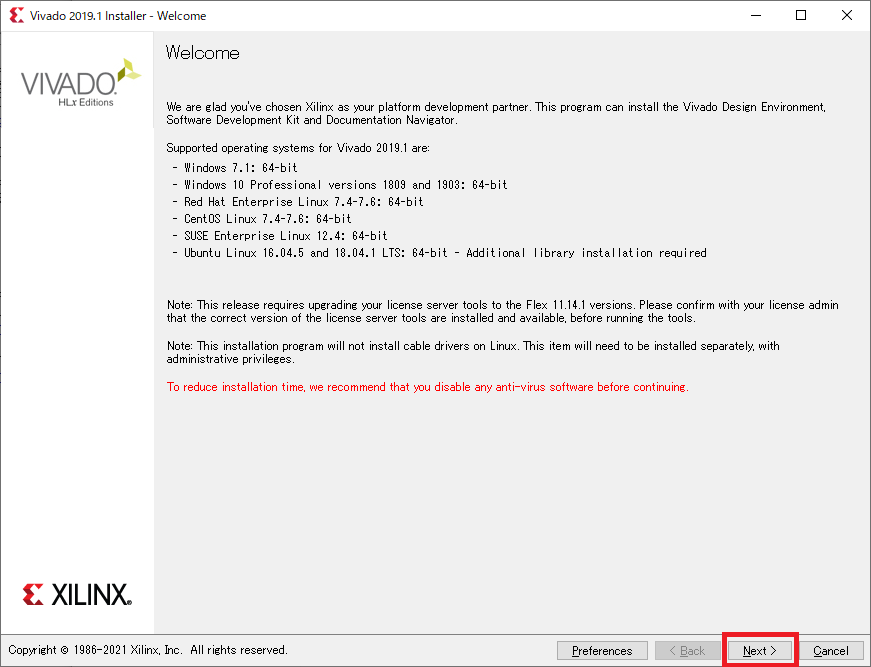

図11の画面ではVivadoをインストールする環境について注釈が出るので,[Next]をクリックします.

図12の画面ではユーザIDとパスワードを入力します(私がインストールしたときはユーザIDとしてXilinx社に登録したメール・アドレスを入力しました).“Download and Install Now”を選択して,[Next]をクリックします.

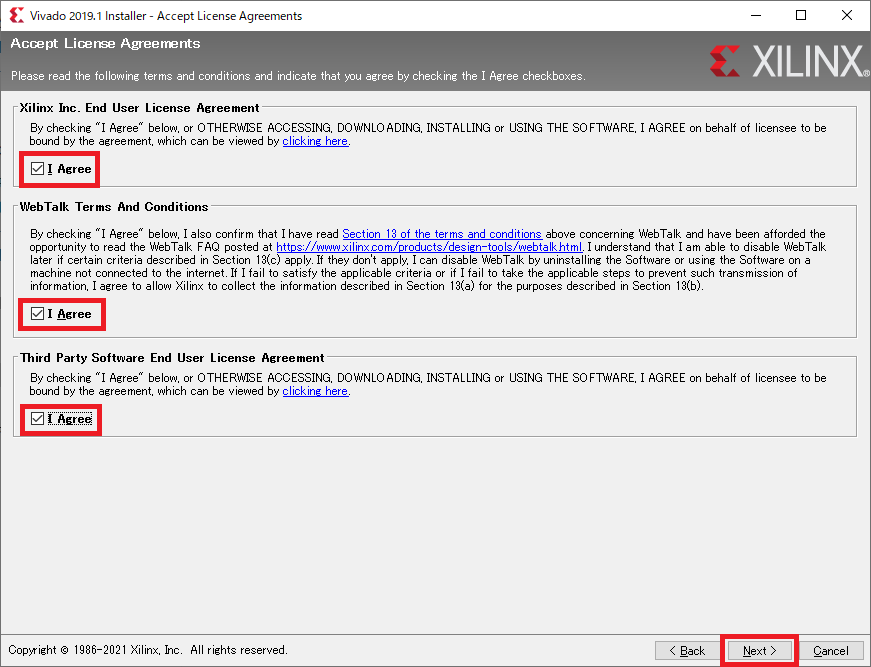

図13の画面ではライセンス関係の同意を求められるので,3箇所にチェックをつけて[Next]をクリックします.

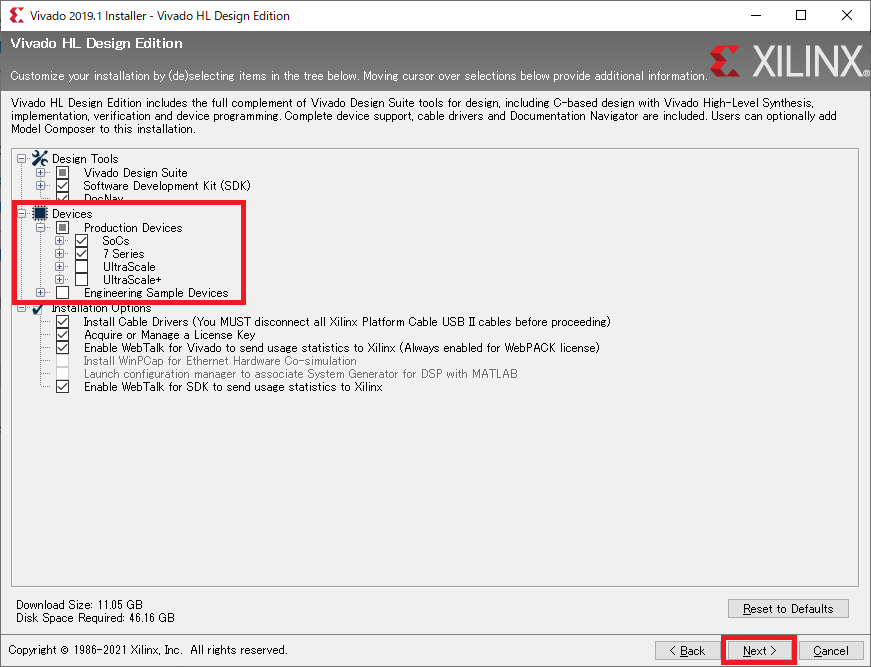

図14の画面ではインストールするエディションを選択します.“Vivado HL Design Edition”にチェックを付けて[Next]をクリックします.

図15の画面では,実際に開発対象とするデバイスを選択します.今回はディスク容量を節約するために,“Devices”の項目の“SoCs”と“7 Series”だけにチェックを付けて,“UltraScale”および“UltraScale+”といった回路規模が大きいデバイスは除外しておきます.それ以外はデフォルトのままにします.

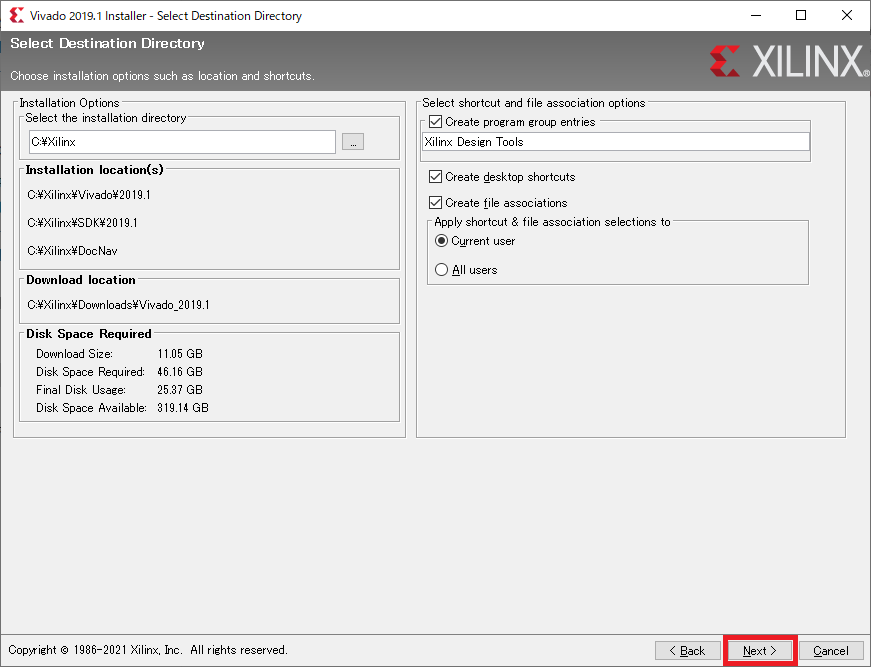

図16の画面ではインストール先のディレクトリを設定できます.今回はデフォルトのままで進めます.

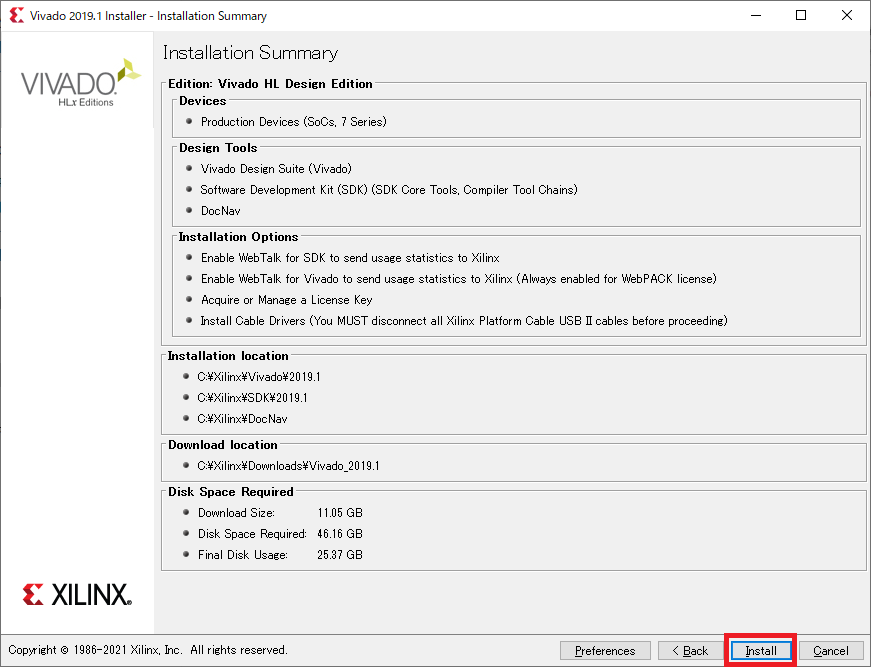

図17の画面では,ここまでの設定の一覧が表示されます.問題ないことを確認して[Install]をクリックします.今回の設定では,11Gバイトのデータをダウンロードします.それなりに時間がかかるので,気長に待ちます(図18).

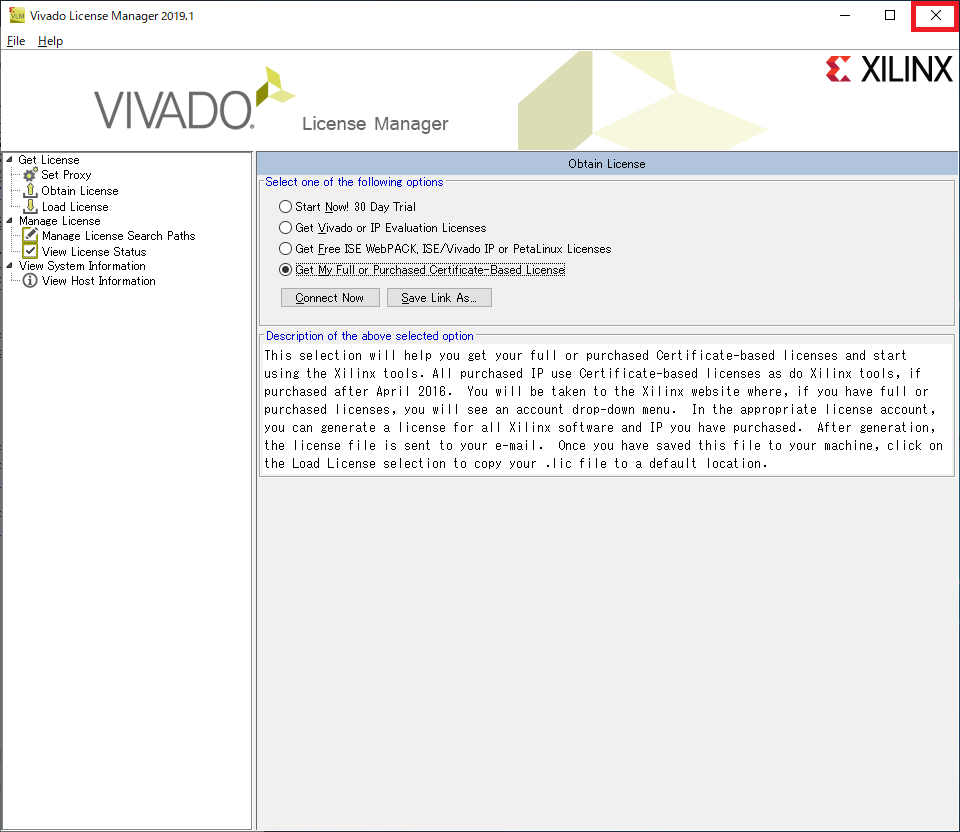

インストールが完了すると,図19のような“Vivado License Manager”の画面が表示されます.今回のEclypse Z7ボード(Zynq-7020デバイス)の開発ではライセンス管理は不要なので,何もせずに閉じてしまって構いません.

Digilent社製ボードのハードウェア情報を入手する

Eclypse Z7ボードの開発元であるDigilent社から,Eclypse Z7ボードのハードウェア情報を記述した“board_files”が提供されています.このboard_filesは後でVivadoで新しいプロジェクトを作るときに利用するので,ここでダウンロードしておきます.

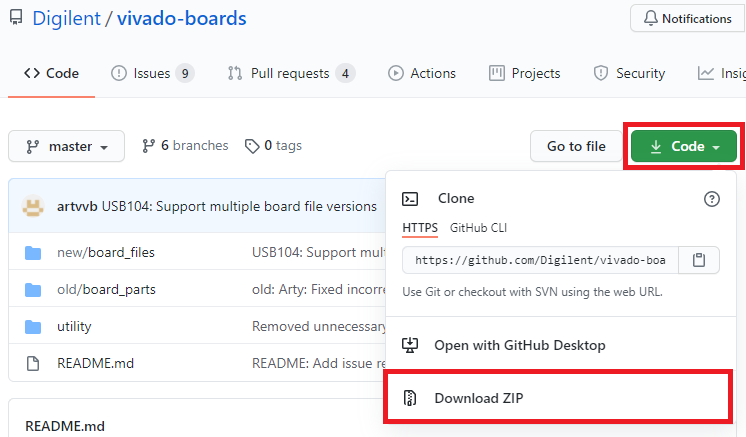

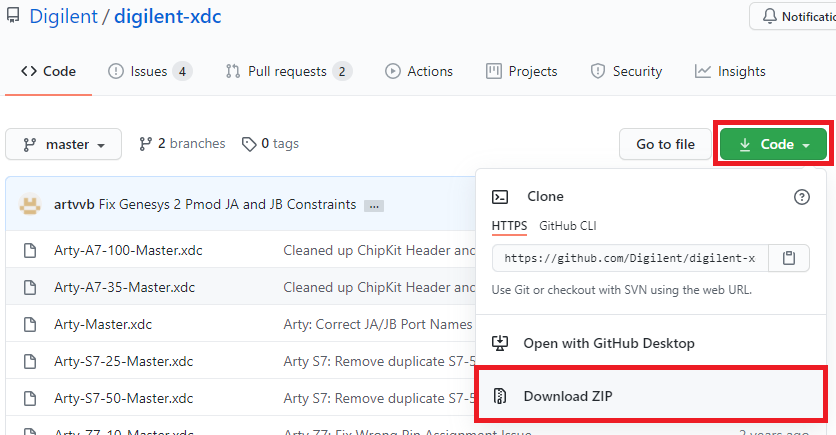

まず,Digilent社製のボードのハードウェア情報が保管されているGitHubのWebページにアクセスします.図20のように“Code”ボタンをクリックして“Download ZIP”をクリックします.

ダウンロードした圧縮ファイルを展開して,“vivado-boards-master/new/board_files/” の中のファイルをすべてコピーします(図21).これらをVivadoのインストール・ディレクトリ内にある“C:/Xilinx/Vivado/2019.1/data/boards/board_files”(デフォルトの場合)に保存します(図22).これでVivadoはEclypse Z7ボードの内部構成を把握できるようになります.

ZynqのFPGA部分(PL)で「Lチカ」の実験をする

Vivadoによる初めてのFPGA開発

Vivadoの使い方に慣れるために,ZynqのFPGA側(PL)に簡単な回路を作り込む練習をしてみます.今回作るのはEclypse Z7ボード上のLEDを点滅させる,いわゆる「Lチカ」の回路です.

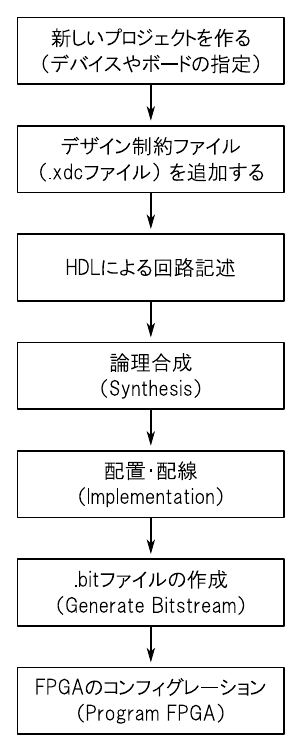

これから行う操作の流れを図23に示します.最初に新しいプロジェクトを作成して,使用するデバイスやボードを選択します.続いて,Zynqの各ピンの割り当てを記述した「デザイン制約ファイル」(“Xilinx Design Constraint”ファイル)を追加します.その後PLの内部に作り込む回路をハードウェア記述言語(HDL)で記述します.今回はHDLとして“Verilog HDL”(以下Verilog)を使います.Verilogによる回路の記述が済んだら「論理合成」,「配置・配線」,「ビットストリーム・ファイル(.bit ファイル)の作成」を行ってZynqに書き込むファイルを作ります.最後にZynqに対してビットストリーム・ファイルを書き込んでコンフィグレーションすれば完了です.

新しいプロジェクトを作る

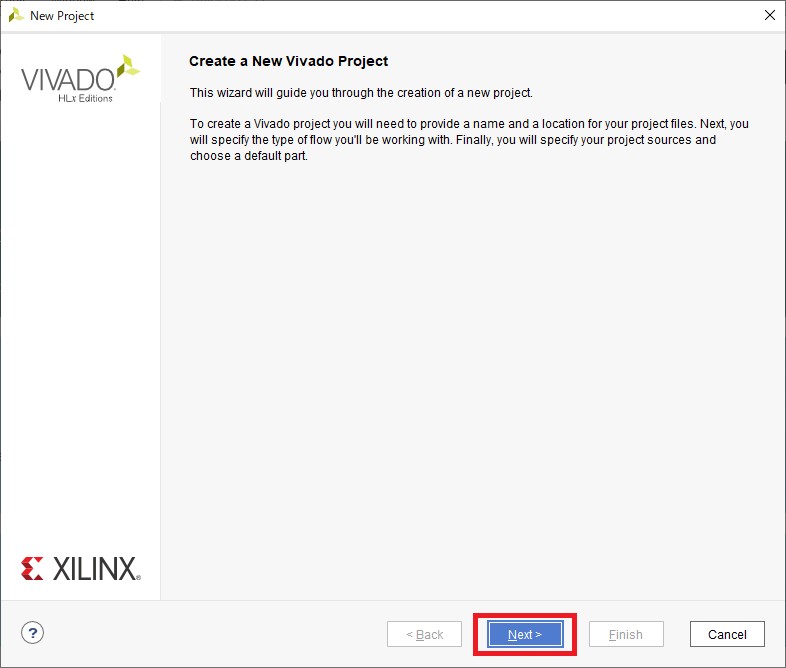

Windowsスタート・メニューから[X] - [Xilinx Design Tools] - [Vivado 2019.1]をクリックしてVivadoを起動します.Vivadoが起動すると図24の画面が表示されるので,[Create Project]をクリックします.続いて表示される図25の画面では[Next]をクリックします.

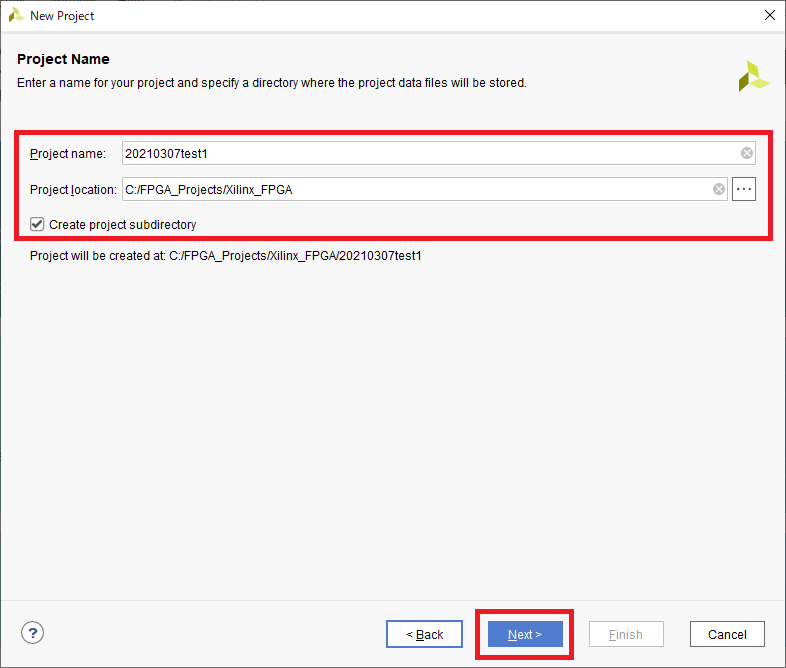

図26の画面ではプロジェクトの名前と保存先を指定します.今回は“20210307test1”というプロジェクト名にしました.プロジェクトを保存するディレクトリは,適宜決めてください.私は今後の実験をまとめて管理するために“C:/FPGA_Projects/Xilinx_FPGA”というディレクトリを作成して,この中に各プロジェクトを保存するようにしています.

なお,“Create project subdirectory”にチェックを付けると,指定したディレクトリ内にプロジェクト名のディレクトリを作成してその中にプロジェクトのファイル群が保存されるようになります.プロジェクトを整理しやすくなるので,チェックを付けておくことをお勧めします.

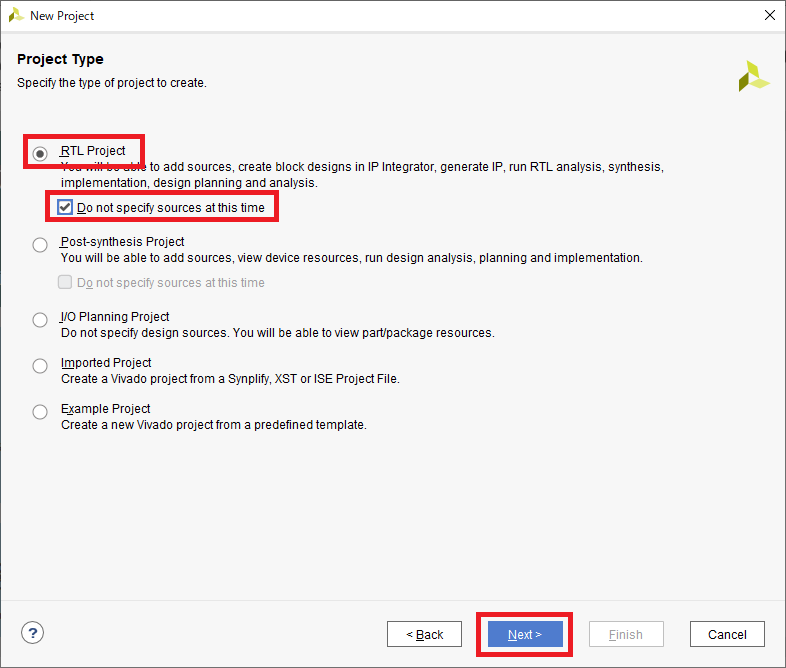

図27の画面ではプロジェクトの種類を指定します.今回は“RTL Project”を選択します.また,今回は既存のファイルがまったく無い状態からプロジェクトを作成するので“Do not specify sources at this time”にチェックを付けておきます.

|

|

|---|---|

| 図26 新規作成するプロジェクトの名前と保存先を指定する | 図27 “RTL Project”を選択する.“Do not specify sources at this time”にチェックを付けておく |

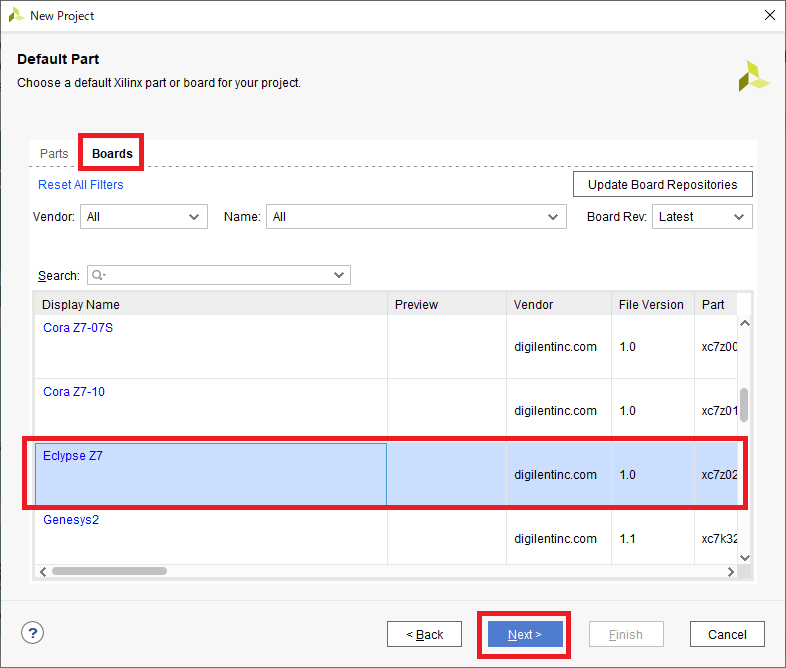

図28の画面では使用するデバイスあるいはボードを選択します.先ほどDigilent社が提供している“board_files”をコピーしておいたので,“Boards”のタブを選択すると一覧の中に“Eclypse Z7”という項目があるはずです.これを選択して[Next]をクリックします.

図29の画面では,新規作成するプロジェクトの設定内容が表示されます.特に問題が無いことを確認して[Finish]をクリックします.

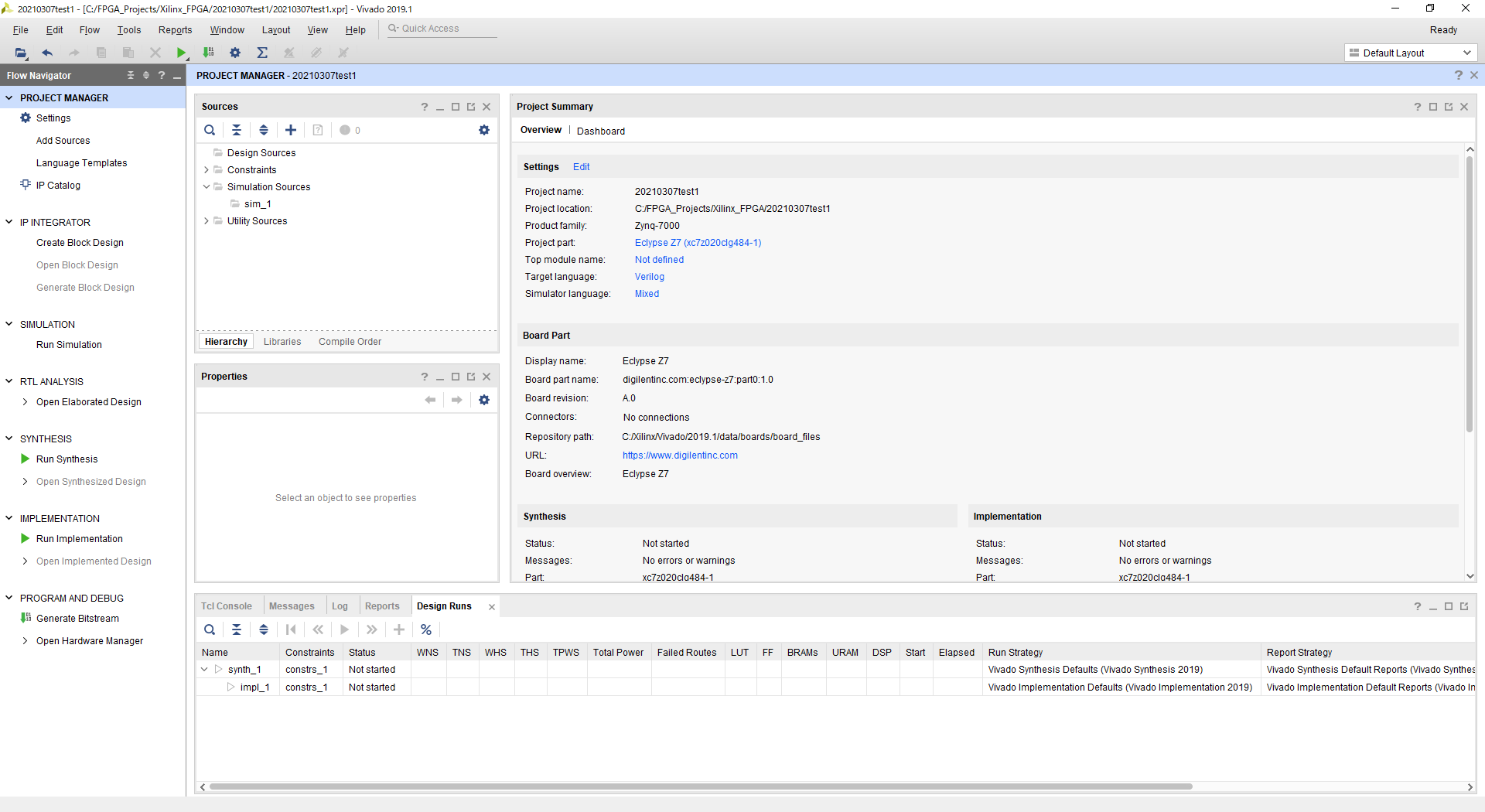

無事にプロジェクトが作成されると,図30の画面が表示されます.これがVivadoの基本画面となります.

.xdcファイルを追加する

Vivadoで扱うデバイスのピン・アサイン(ピン割り当て)情報は,“Xilinx Design Constraints File”(ザイリンクス・デザイン制約ファイル)によって管理されています.拡張子は“.xdc”です.Eclypse Z7ボード上のZynqのピン・アサインに関する情報は,あらかじめDigilent社が用意してくれています.このデータが保管されているGitHubのWebページにアクセスして,ZIPファイルをダウンロードします(図31).ダウンロードしたファイルを展開して,わかりやすい場所に保存しておきます.

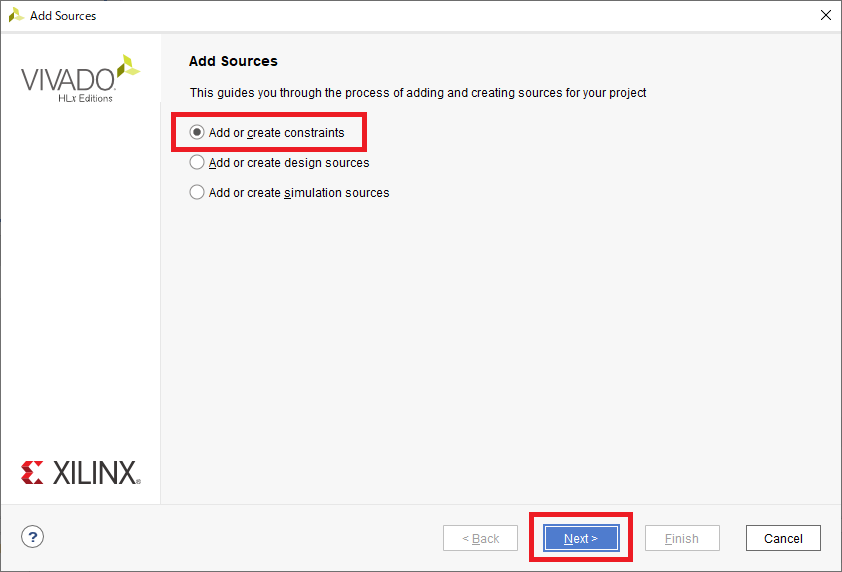

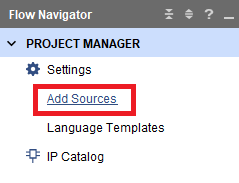

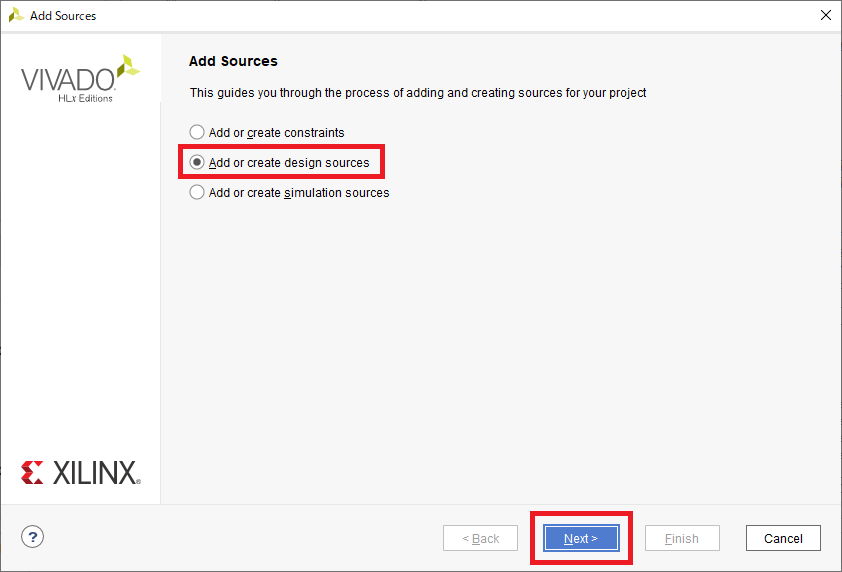

ダウンロードした.xdcファイルをプロジェクトに追加します.Vivadoの画面左側の“Flow Navigator”の中から“Add Sources”をクリックします(図32).すると図33の画面が表示されるので“Add or create constraints”を選択して[Next]をクリックします.

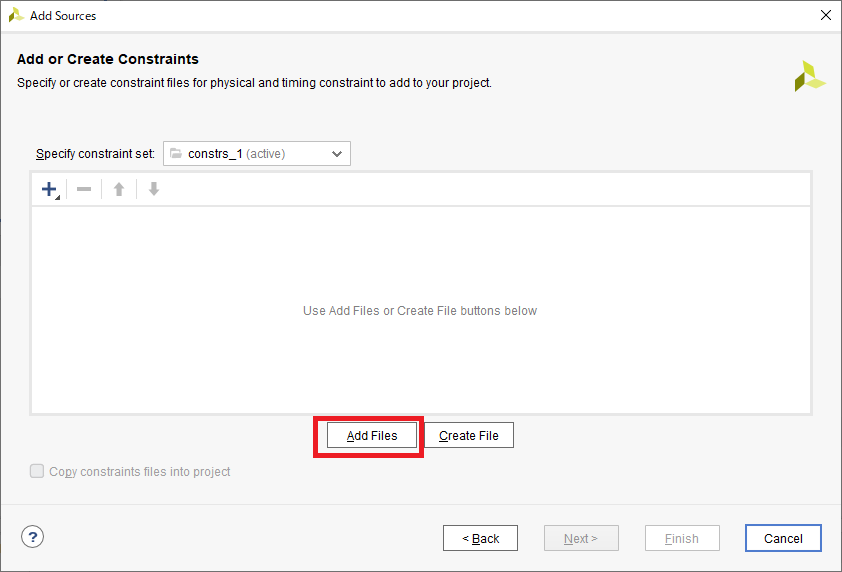

図34の画面で“Add Files”をクリックします.すると図35のようにファイル・ブラウザが表示されるので,さきほどGitHubからダウンロードして展開しておいたディレクトリへ移動します.この中から“Eclypse-Z7-Master.xdc”を選択して[OK]をクリックします.

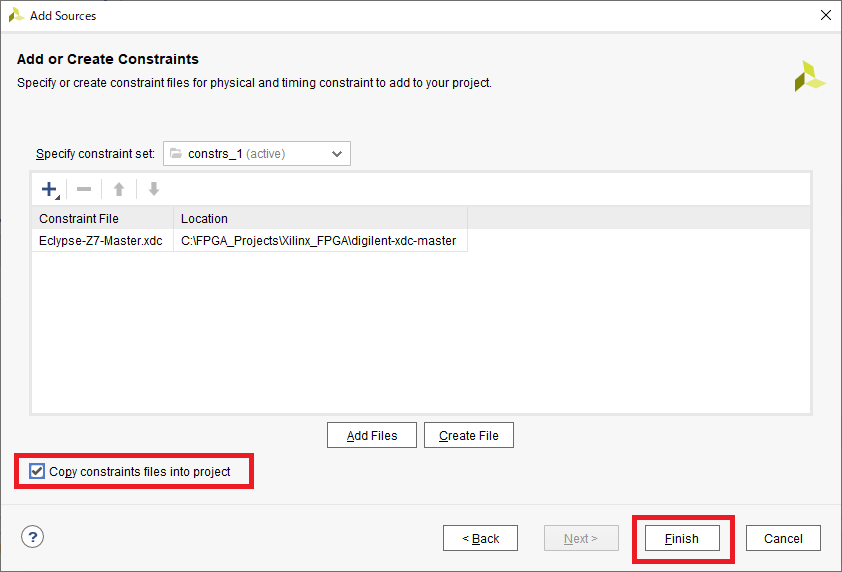

図36の画面に戻るので,“Copy constraints file into project”にチェックを付けて[Finish]をクリックします.このオプションにチェックを付けておくと,元の.xdcファイルをコピーしたものがプロジェクトのディレクトリ内に保存されるます.オリジナルの.xdcファイルが変更されることを防げるので,チェックを付けておくことをお勧めします.

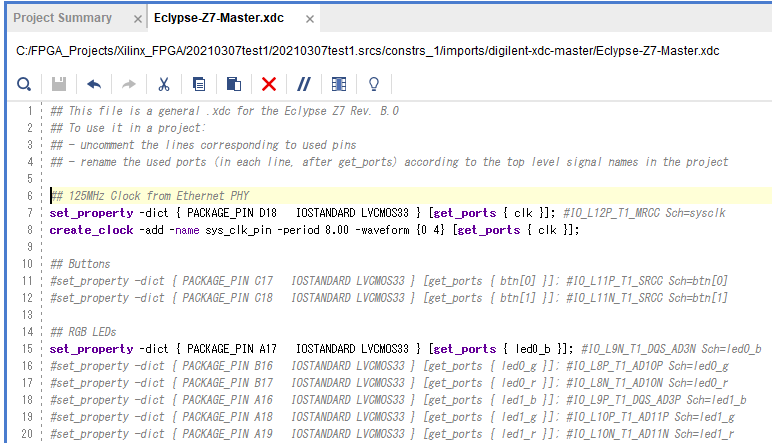

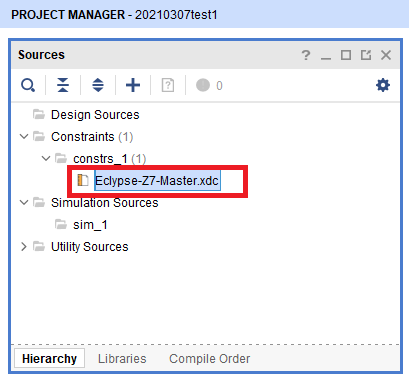

.xdcファイルを追加できたら,図37のようにVivadoの“Source”エリアにある“Constraints”を展開して“Eclypse-Z7-Master.xdc”があることを確認します.これをダブルクリックすると,.xdcファイルの編集画面が開きます.

|

|

|---|---|

| 図36 “Copy constraints file into project”にチェックを付けて[Finish]をクリックする | 図37 “Sources”エリアの“Constraints”の中にあるEclypse Z7ボードの.xdcファイルをダブル・クリックして開く |

図38の編集画面で,.xdcファイルを次のように編集します.まず,125 MHzのクロック信号が入力されるピンをアクティブにするために,7行目と8行目をコメント・アウトしている“#”を削除します.さらに,LEDに接続されているピンもアクティブにします.今回は15行目の文頭の“#”を削除して“led0_b”を有効にしました.これで“LED0”(基板上のシルクは“LD0”)の青色LEDに接続されているZynqのピンが有効になります.

Verilogファイルを追加する

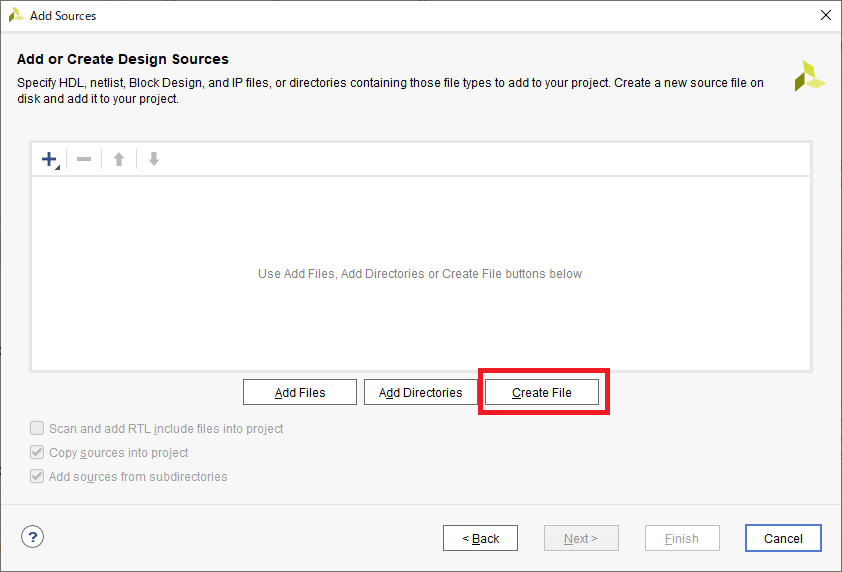

FPGA(PL)に作り込む論理回路を設計します.図39のように“Add Sources”をクリックします.続いて表示される図40の画面では“Add or create design sources”を選択して[Next]をクリックします.

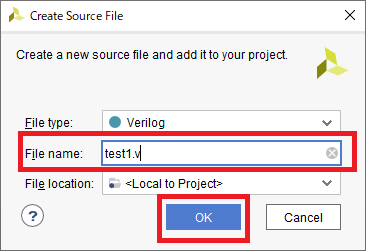

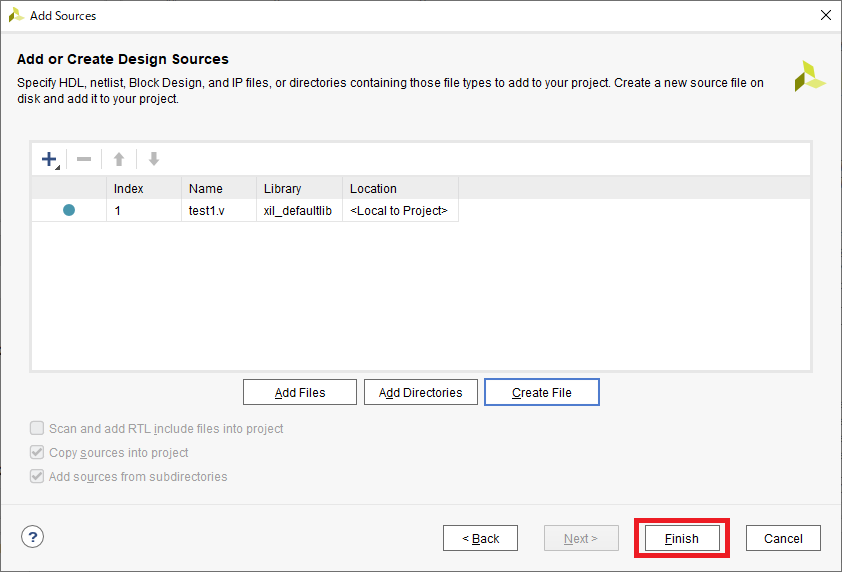

図41の画面で“Create File”をクリックします.図42の画面ではFile typeの欄で“Verilog”を選び,File nameの欄にファイル名を入力します.今回は“test1.v”としました.Verilogファイルなので,拡張子は“.v”です.

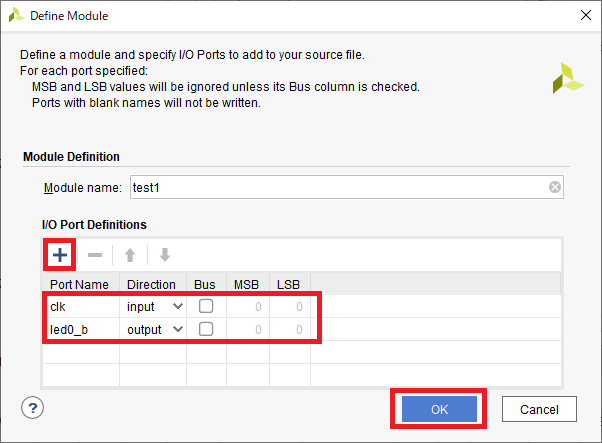

図43の画面が表示されたら[Finish]をクリックします.続いて図44の画面が表示されるので,これから作るモジュールの入出力ポートを定義しておきます.[+]ボタンをクリックして,2個の入力欄を用意します.1つめの入力欄はPort Nameを“clk”,Directonは“input”に設定します(外部から125 MHzのクロックを入力するポート).2つめの入力欄はPort Nameを“led0_b”,Directionを“output”にします(青色LEDに接続するポート).

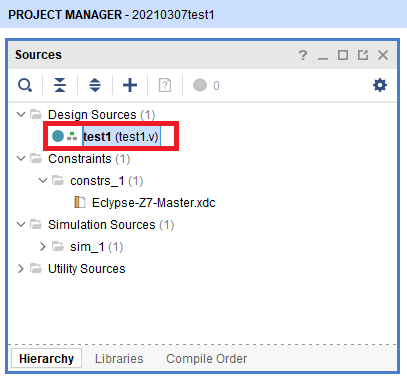

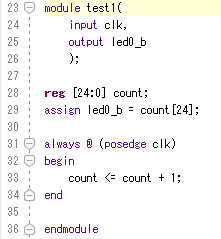

Vivadoの画面に戻ったら,図45のように“Sources”エリアの“Design Sources”を展開します.いま作成した“test1.v”があることを確認し,ダブル・クリックして開きます.Verilogファイルの編集画面が開くので,リスト1の内容を記述します.記述し終わった状態を図46に示します.

|

|---|

| リスト1 LED点滅回路のVerilog記述例“test1.v” |

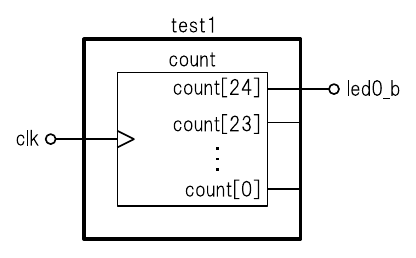

ここで定義している論理回路は図47のように非常に単純なものです.25ビット幅のレジスタ“count”を用意して,“clk”信号の立ち上がりエッジで値をインクリメントしています.出力の“led0_b”は“count”レジスタの25ビット目をそのまま接続しています.これで,Zynqの外部から入力される125 MHzのクロックを分周した信号がLEDに印加されるようになります.

論理合成および配置・配線を実行する

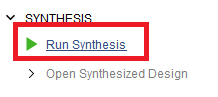

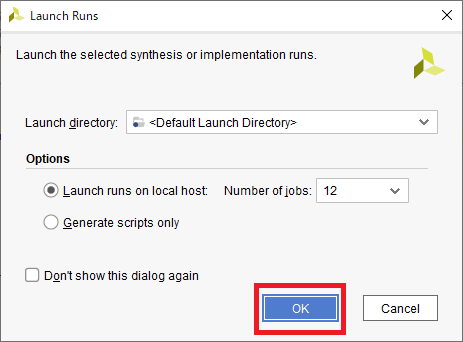

Verilogによる回路記述ができたら,「論理合成」(synthesis)を実行します.図48に示すとおり,画面左側の“Flow Navigator”の中の“Run Synthesis”をクリックします.図49の画面では“Launch runs on local host”を選択し,論理合成に使用するプロセッサのコア数(自分の環境の最大値がおすすめ)を設定して[OK]をクリックします.

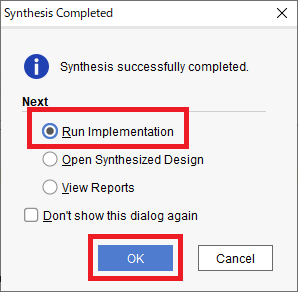

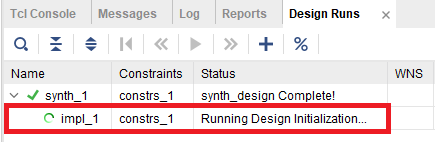

図50のように画面下部の“Design Runs”タブに論理合成中の様子が表示されるので,完了するまで待ちます.論理合成が完了すると図51のように次の動作を質問されるので,「配置・配線」(implementation)を実行します.

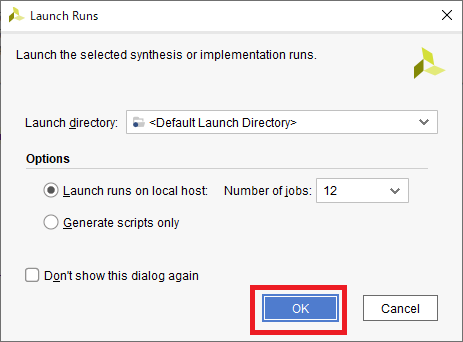

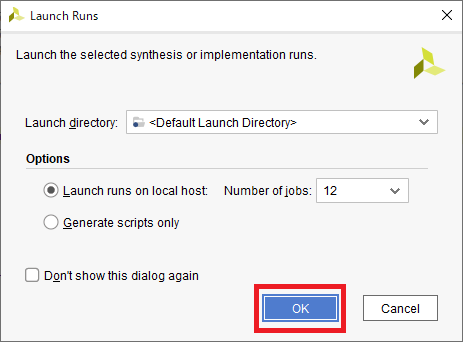

図52の画面では,例によってプロセッサ数を設定して[OK]をクリックします.配置・配線が完了するまで少し待ちます(図53).

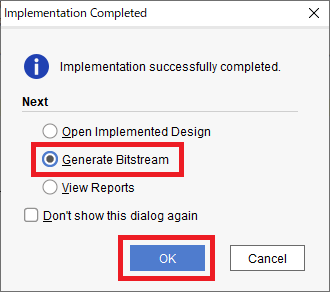

配置配線が完了したら,Zynqに書き込むPLの定義ファイルである「ビットストリーム」(bitstream)を作成します.配置配線が完了した後に表示される図54の画面で“Generate Bitstream”を選択して[OK]をクリックします.図55の画面ではビットストリームの作成に使用するプロセッサのコア数を設定して[OK]をクリックします.

ビットストリームの作成が完了すると,Vivadoの画面の右上に“write_bitstream Complete”と表示されます.

ZynqのPLにデータを書き込む

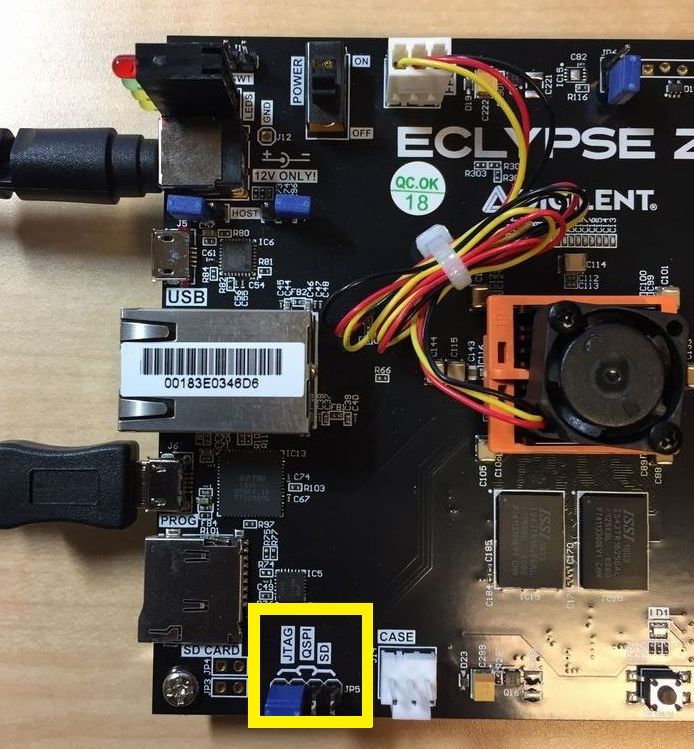

完成したビットストリームをZynqに書き込みます.Eclypse Z7ボードに付属のACアダプタを接続します.また,付属のUSB Type A - micro B ケーブルを使ってEclypse Z7ボードの“J6”コネクタ(シルクで“PROG”と書かれている)とPCを接続します.ボード上のジャンパ“JP5”は,写真5のように“JTAG”側にします.なお,“JTAG”(Joint Test Action Group)とはCPUやFPGAに対して書き込みやデバッグをするための規格の1つです.この状態でEclypse Z7ボードの“POWER”スイッチを“ON”します.

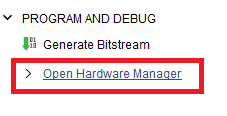

Eclypse Z7ボード側の準備ができたら,図56のようにVivadoの画面左側の“Flow Navigator”の中の“Open Hardware Manager”をクリックします.初めてこの操作を実行したときは図57の画面が出るので,適宜チェックをつけて[アクセスを許可する]をクリックします.

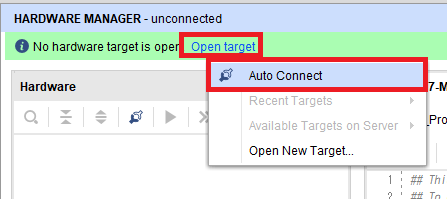

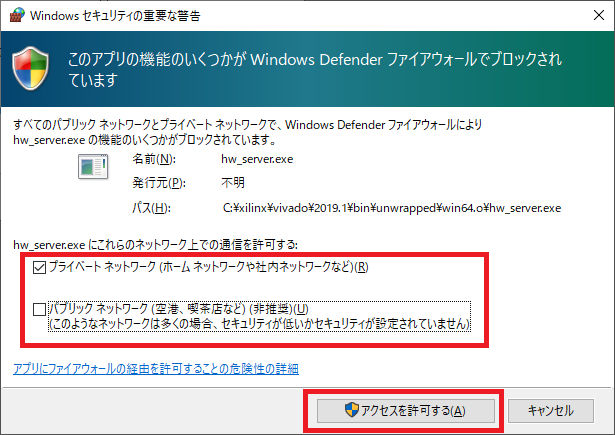

画面の上部に“No hardware target is open”と表示されるので“Open target”をクリックし,“Auto Connect”をクリックします(図58).ここでも初回は図59のようにアクセス許可を求める画面が出るので,適宜チェックを入れて[アクセスを許可する]をクリックします.

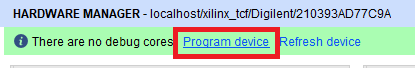

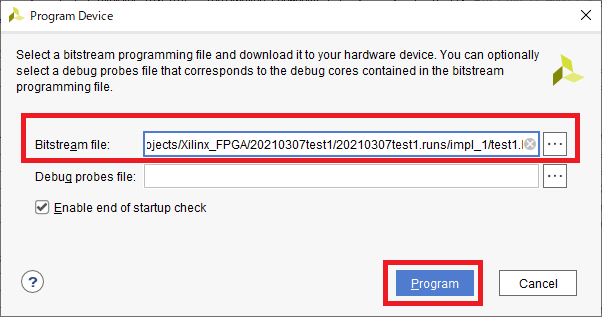

問題なくEclypse Z7ボードとの接続が確立されると図60のように“Program device”と表示されるので,これをクリックします.もし表示されない場合は,ボードの電源やUSBケーブルの接続,“JP5”のジャンパが“JTAG”側になっていることなどを確認してください.図61の画面では先ほど作成したビットストリームが選択されていることを確認し,[Program]をクリックします.

ビットストリームの書き込み後,ボード上のLED“LD0”が青色で点滅すれば成功です(写真6).なお,今回はJTAGでビットストリームを転送しているので,ボードの電源を切るとFPGAのコンフィグレーションは初期化されてしまいます.電源を切ってもコンフィグレーションを維持するためにはZynqのPS側と連携する必要があります.この内容は追って説明します.