FPGA×HDL入門 基本は全レジスタ同期運転

クロック源は1つ 同一位相&同一周波数

Artix-7 FPGA入門 基本は全レジスタ同期運転

|

|---|

|

図1 レジスタの同期運転は,信頼性の高い回路を構築するための基本だ.同一クロック源を用い,レジスタの値を同期的に更新することを徹底することで,設計が簡単になりエラーの発生率も低下する.画像クリックで動画を見る.または記事を読む.[提供・著]森岡 澄夫

詳細:[VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門 |

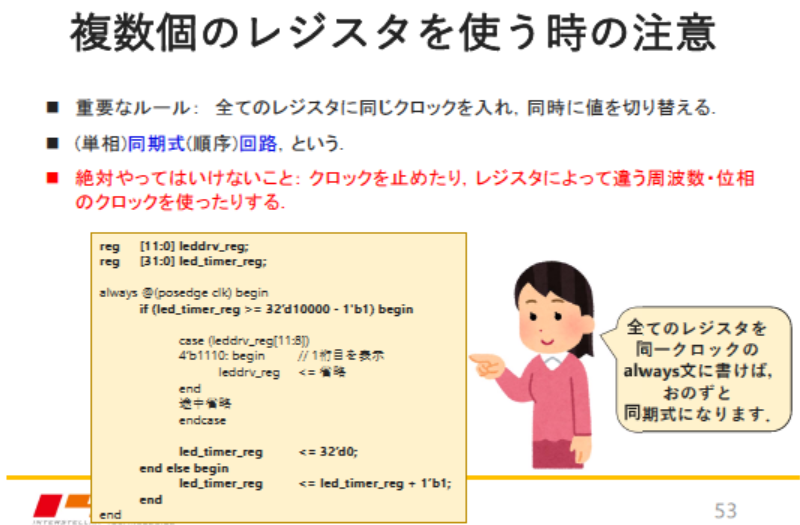

同期式回路設計の基礎

すべてのレジスタは同一クロックで動作し,値は同期的に切り替えることことで,ディジタル回路の挙動が予測可能になり,動作の信頼性が向上します.

以下のポイントを守る必要があります.

- 単一のクロック源を使用する

レジスタ間でクロックの位相や周波数が異なる場合,意図しない動作やタイミング・エラーが発生する可能性があります - レジスタをalways文で制御する

次のように書くことで、すべてのレジスタを単一クロックで駆動し、同期式設計が可能です:

reg [11:0] leddrv_reg; reg [31:0] led_timer_reg; always @(posedge clk) begin if (led_timer_reg >= 32'd10000 - 1'b1) begin case (leddrv_reg[11:8]) 4'b1110: leddrv_reg <= /* 新しい値 */; endcase led_timer_reg <= 32'd0; end else begin led_timer_reg <= led_timer_reg + 1'b1; end end上記コードでは、すべてのレジスタ値がクロックの立ち上がり(

posedge)で一斉に更新されます。

同期式回路における注意点

同期式回路の設計では,以下の行為を避ける必要があります.

- クロックを止める

レジスタの値を保持したい場合は,クロックを止めるのではなく,現在の値を再ロードする設計にします.以下は値を保持する設計例です.reg [7:0] reg_a; always @(posedge clk) begin reg_a <= reg_a; // 値を保持 end - 複数クロックを使用する

各レジスタに異なるクロックを使用すると,同期の乱れや信号遅延が生じ,設計の予測性が失われます.

全レジスタ同期運転における「クロックの統一」の重要性

FPGAにおけるディジタル回路設計では,クロックの統一が極めて重要です.以下のような理由があります.

1.タイミング・エラーの防止

複数クロックを使用すると,レジスタ間のデータ遷移タイミングが崩れる可能性があります.例えば,異なる周波数や位相のクロックを用いた場合,特定のタイミングで信号が正しく伝達されず,設計が意図しない動作をする可能性があります.

2.設計の簡略化

単一クロック源を使用すると,設計時の考慮事項が減少し,シミュレーションやデバッグが容易になります.たとえば,次のレジスタ更新ルールを守ることで,設計の安定性を確保できます.

- $A$と$B$の2つのレジスタがあり,クロックごとにそれぞれ値が更新される場合

- $A$には毎クロック$1$を加算

- $B$には最新の$A$の値を加算

以下にクロックごとの$A$と$B$の変化を示します.すべての値はクロックごとに同期的に変化します.

| クロック | $A$ | $B$ |

|---|---|---|

| 初期値 | 1 | 2 |

| 1クロック後 | 2 | 3 |

| 2クロック後 | 3 | 5 |

| 3クロック後 | 4 | 8 |

| 4クロック後 | 5 | 12 |

| 5クロック後 | 6 | 17 |

3.信号の再利用性

同期的な回路では,信号が次のクロックで確実に更新されるため,予測可能な動作が可能です.この特性を利用して,設計全体のモジュール化や再利用性を向上させることができます.

まとめ

FPGA設計におけるレジスタの同期運転は,信頼性の高い回路を構築するための基本です.同一クロック源を用い,レジスタの値を同期的に更新することを徹底しましょう.この原則を守ることで,設計が簡単になり,エラー発生率が低下します.〈著:ZEPマガジン〉

〈著:ZEPマガジン〉著者紹介

- NTT,IBM,Sony,NECの各研究所において高性能回路IPやハイレベル・シンセシスの研究,およびプレイステーションなどの製品用SoC開発に従事した後,現職にて民間宇宙ロケットの飛行制御コンピュータの研究開発に従事.FPGAや高位合成を活用している

著書

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD/KIT]Tiny FPGA実習!高校生から始めるHDLプログラミング,ZEPエンジニアリング株式会社.

- [VOD/Pi KIT]カメラ×ラズパイで一緒に!初めての画像処理プログラミング,ZEPエンジニアリング株式会社.

- スパコンでも破れない!高セキュリティ・マイコン・プログラミング,ZEPエンジニアリング株式会社.

- [YouTube]宇宙軌道ロケット 成功の方程式

- [YouTube]宇宙ロケットの電子回路開発

- FPGA/Zynqで作るカスタム・コンピュータ・チップ,ZEPエンジニアリング株式会社.

- Lチカ入門!ソフトウェア屋のためのHDL事はじめ,ZEPエンジニアリング株式会社.

- USBカメラの動画キャプチャ&描画用 Pythonプログラム,ZEPエンジニアリング株式会社.

- ライブラリ完備!組立式ラズパイI/O増設ボード MCC DAQ HATSファミリ誕生,ZEPエンジニアリング株式会社.

参考文献

- [VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門,ZEPエンジニアリング株式会社.