FPGA×HDL超入門 4桁の7segLED制御

4個の桁用レジスタ+8個の数字用レジスタで構成

4桁の7セグメントLED制御回路のVerilog HDLソース

|

|---|

|

図1 Verilog HDLでは,`reg`で宣言されるレジスタは,次のクロック立ち上がり時に値を保持する重要な役割を果たす.4桁7セグメントLEDの制御回路の正しい記述は?.画像クリックで動画を見る.または記事を読む.[提供・著]森岡 澄夫

詳細:[VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門 |

1.レジスタを用いた基礎的なHDL設計

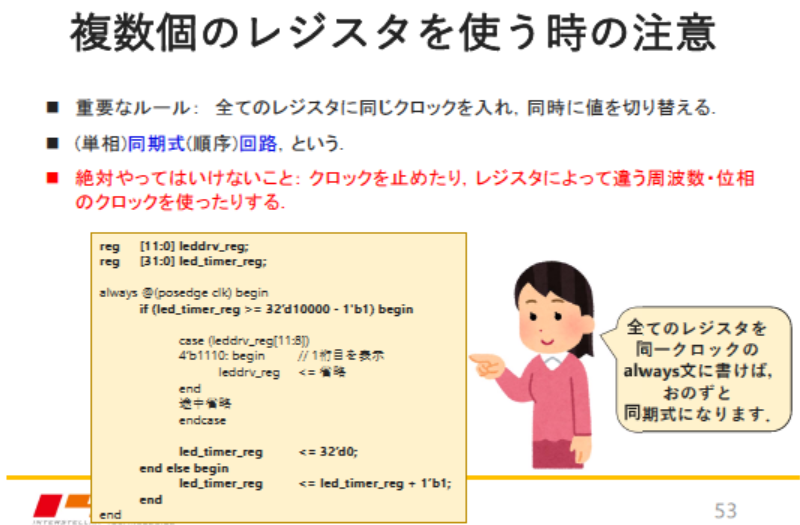

FPGAを用いて4桁の7セグメントLEDを制御する際,重要な要素は「レジスタ」と「クロック」です.Verilog HDLでは,`reg`で宣言されるレジスタは次のクロック立ち上がり時に値を保持する役割を果たします.

以下のようなコードは16ビット・カウンタを定義します.

reg [15:0] cnt_reg;

always @(posedge clk) begin

cnt_reg <;= cnt_reg + 1'b1;

end

注意すべき点は`<=`(ノンブロッキング代入)を使用することです.これにより,クロックに同期した動作が保証されます.非同期動作の可能性がある`assign`文とは異なり,`always`ブロック内では`<=`を用いるのが通例です.

2.桁切り替えの基本設計

FPGAでの7セグメントLED制御では,各桁を順次切り替えて表示します.このプロセスを実現するのが`led_drv_reg`というレジスタです.

以下のコードでは4桁の切り替えを行います.

reg [11:0] led_drv_reg;

always @(posedge clk) begin

case (led_drv_reg[11:8])

4'b1110: led_drv_reg <= {4'b1101, SEG7_LUT(sw[7:4], 1'b1), 1'b1};

4'b1101: led_drv_reg <= {4'b1011, SEG7_LUT(sw[11:8], 1'b1), 1'b1};

4'b1011: led_drv_reg <= {4'b0111, SEG7_LUT(sw[15:12], 1'b1), 1'b1};

default: led_drv_reg <= {4'b1110, SEG7_LUT(sw[3:0], 1'b1), 1'b1};

endcase

end

`led_drv_reg[11:8]`は現在表示する桁を指定し,それに基づきLEDに表示される値が設定されます.また,`SEG7_LUT`関数を用いることでトグル・スイッチ(`sw`)の入力値に応じたセグメント・パターンが決定されます.

切り替え速度が速すぎる場合,100MHzのような高周波数では各桁の表示が残像として重なり,認識が困難になることがあります.この問題を解決するには,カウンタを追加して桁切り替え速度を低下させる必要があります.

3.連接(Concatenation)の有効活用

Verilogにおいて,連接(concatenation)は複数のビットを1つの値としてまとめる強力な手法です.例えば,以下の記述は12ビットの新しい値を生成しています.

led_drv_reg <;= {4'b1101, SEG7_LUT(sw[7:4], 1'b1), 1'b1};

- 上位4ビット(`4'b1101`):表示対象の桁

- 中位7ビット(`SEG7_LUT`の出力):セグメントデータ

- 下位1ビット(`1'b1`):ドット(小数点)の点灯状態

これらを連結することで,一度に12ビットの値を生成しています.この手法により,複数の信号を効率よく1つのレジスタにまとめることが可能になります.切り替えやデータ送信のような処理では連接を適切に活用することでコードの可読性と効率性が向上します.〈著:ZEPマガジン〉

著者紹介

- NTT,IBM,Sony,NECの各研究所において高性能回路IPやハイレベル・シンセシスの研究,およびプレイステーションなどの製品用SoC開発に従事した後,現職にて民間宇宙ロケットの飛行制御コンピュータの研究開発に従事.FPGAや高位合成を活用している

著書

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD/KIT]Tiny FPGA実習!高校生から始めるHDLプログラミング,ZEPエンジニアリング株式会社.

- [VOD/Pi KIT]カメラ×ラズパイで一緒に!初めての画像処理プログラミング,ZEPエンジニアリング株式会社.

- スパコンでも破れない!高セキュリティ・マイコン・プログラミング,ZEPエンジニアリング株式会社.

- [YouTube]宇宙軌道ロケット 成功の方程式

- [YouTube]宇宙ロケットの電子回路開発

- FPGA/Zynqで作るカスタム・コンピュータ・チップ,ZEPエンジニアリング株式会社.

- Lチカ入門!ソフトウェア屋のためのHDL事はじめ,ZEPエンジニアリング株式会社.

- USBカメラの動画キャプチャ&描画用 Pythonプログラム,ZEPエンジニアリング株式会社.

- ライブラリ完備!組立式ラズパイI/O増設ボード MCC DAQ HATSファミリ誕生,ZEPエンジニアリング株式会社.

参考文献

- [VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門,ZEPエンジニアリング株式会社.