FPGAキット DE10入門 正しく動かない乗算器

間違いだらけのverilog記述

正しい演算の重要な設定「ビット幅

|

|---|

|

図1 正しく動かない演算が生成される問題を回避するためには,ビット幅を明示的に指定し,意図しない切り捨てや拡張を避けるverilogを記述することが重要.画像クリックで動画を見る.または記事を読む.[提供・著]森岡 澄夫

詳細:[VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】 |

Verilog記述のよくある「間違い」

Verilog HDLでの演算記述は,一見理解しやすいように思えますが,細かな仕様に注意しなければ,意図したとおりに動作しない回路が生成されることがあります.

上記動画の「正しく動かない乗算器」の原因は,演算ビット幅の扱いに起因しています.

次のような記述があります.

```verilog wire [7:0] mult_out = mult_in0 * mult_in1; ```

一見問題なさそうに見えますが,実際には演算結果のビット幅が左辺の`[7:0]`に制限されてしまい,上位ビットが切り捨てられる場合があります.この仕様を理解しないまま設計すると,期待した結果が得られないばかりか,デバッグに多大な時間を要する可能性があります.

演算ビット幅の基本原則

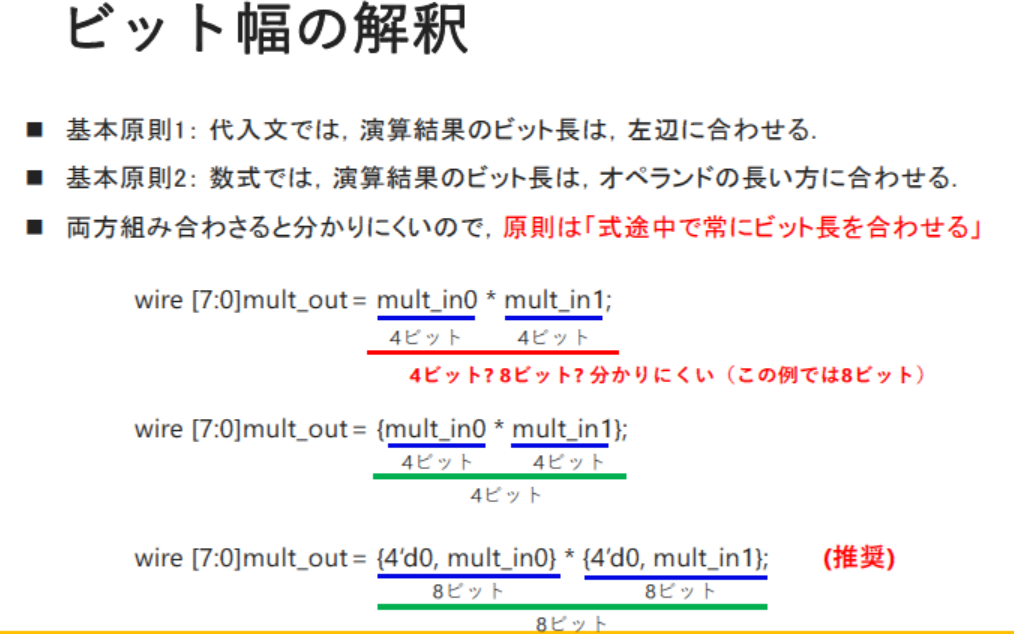

Verilogの演算におけるビット幅のルールは次の2つです.

- 代入文では,演算結果のビット長は左辺に合わせる.`wire [7:0] mult_out`に代入される場合,演算結果が8ビットに切り詰められます

- 数式では,演算結果のビット長はオペランドの長い方に合わせる.`mult_in0`と`mult_in1`が4ビットなら演算結果は4ビットですが,一方が8ビットであれば演算結果も8ビットになります.

これらのルールが複雑に組み合わさることで,ビット幅の解釈がさらに難解になります.

演算結果を正しく扱うための工夫

「演算が正しく動かない」問題を防ぐには,ビット幅を明示的に指定し,意図しない切り捨てや拡張を避けることが重要です.次の2点を意識するとよいでしょう.

- オペランドのビット幅を統一する

オペランドが異なるビット幅をもつ場合,意図した結果が得られないことがあります.たとえば次のようにビット幅を揃えておくことで,意図しない結果を防ぐことができます. ```verilog wire [7:0] mult_in0_ext = {4'd0, mult_in0}; wire [7:0] mult_in1_ext = {4'd0, mult_in1}; wire [7:0] mult_out = mult_in0_ext * mult_in1_ext; ``` - 論理合成結果を確認する

演算結果がRTLシミュレーションで期待とおりに見えても,実際のFPGA上では異なる動作をする場合があります.論理合成後の回路図を確認する習慣をつけることが重要です

「代入文」と「数式」に潜むビット幅の落とし穴

Verilog HDLでは,ビット幅の扱いにおいて「代入文」と「数式」に異なるルールが適用されるため,誤解を招きやすい設計ミスが発生します.この節では,特に注意が必要な点を解説します.

ビット幅の切り詰め

次の記述を考えてみましょう: ```verilog wire [7:0] mult_out = mult_in0 * mult_in1; ```

`mult_in0 * mult_in1`の演算結果が8ビットを超える場合でも,左辺のビット幅`[7:0]`に合わせて上位ビットが切り捨てられます.`mult_in0 = 255`,`mult_in1 = 255`である場合,本来の演算結果は65535(16ビット)が期待されますが,結果は下位8ビット(255)だけが保持されます.

ビット幅の拡張

次の記述を見てみます:

```verilog wire [7:0] mult_out = {mult_in0 * mult_in1}; ```

演算結果は暗黙的にビット幅が拡張され,意図しない動作を引き起こす可能性があります.意図した動作を実現するためには,演算前にオペランドのビット幅を揃えておくことが推奨されます.

〈著:ZEPマガジン〉著者紹介

- NTT,IBM,Sony,NECの各研究所において高性能回路IPやハイレベル・シンセシスの研究,およびプレイステーションなどの製品用SoC開発に従事した後,現職にて民間宇宙ロケットの飛行制御コンピュータの研究開発に従事.FPGAや高位合成を活用している

著書

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編】,ZEPエンジニアリング株式会社.

- [VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作,ZEPエンジニアリング株式会社.

- [VOD/KIT]Tiny FPGA実習!高校生から始めるHDLプログラミング,ZEPエンジニアリング株式会社.

- [VOD/Pi KIT]カメラ×ラズパイで一緒に!初めての画像処理プログラミング,ZEPエンジニアリング株式会社.

- スパコンでも破れない!高セキュリティ・マイコン・プログラミング,ZEPエンジニアリング株式会社.

- [YouTube]宇宙軌道ロケット 成功の方程式

- [YouTube]宇宙ロケットの電子回路開発

- FPGA/Zynqで作るカスタム・コンピュータ・チップ,ZEPエンジニアリング株式会社.

- Lチカ入門!ソフトウェア屋のためのHDL事はじめ,ZEPエンジニアリング株式会社.

- USBカメラの動画キャプチャ&描画用 Pythonプログラム,ZEPエンジニアリング株式会社.

- ライブラリ完備!組立式ラズパイI/O増設ボード MCC DAQ HATSファミリ誕生,ZEPエンジニアリング株式会社.

参考文献

- [VOD/KIT] 実習キットで一緒に作る!オープンソースCPU RISC-V入門,ZEPエンジニアリング株式会社.

- [VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門,ZEPエンジニアリング株式会社.