A-Dコンバータと高性能プロセッサをつなぐ超高速I/F“JESD204”

計測のためのA-Dコンバータ実装術

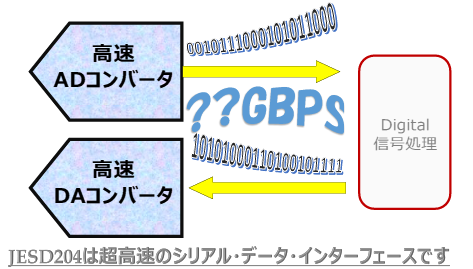

A-D/D-Aコンバータとディジタル処理系の接続課題

|

|---|

|

図1 12ビット/100MspsのA-Dコンバータでも,通信のために単純計算で1.2Gbpsのデータ容量が必要.この量のデータを確実に受け渡すためには,信号の整合性や同期精度に優れた高速インターフェースが必要.画像クリックで動画を見る.または記事を読む.[著]藤森 弘己 詳細:[VOD]高速&エラーレス!5G×EV時代のプリント基板&回路設計 100の要点 |

高速なA-DコンバータやD-Aコンバータを用いたシステムでは,変換されたデータを高速かつ確実に処理系へ伝送する必要があります. A-Dコンバータは入力されたアナログ信号をディジタルデータに変換し,FPGAやSoCなどの演算装置に出力します. 一方,演算処理後のデータはD-Aコンバータに送られて再びアナログ信号へと変換されます. この往復の中でもっとも重要な要素が,ADCやDACとディジタル側を接続するインターフェースです.

膨大なデータ量とGbps級の伝送ニーズ

例として12ビットの解像度で100Mspsのサンプリング速度をもつA-Dコンバータを想定した場合,単純な計算でも1.2Gbpsのデータ量になります. この規模のデータを確実に受け渡すためには,信号の整合性や同期精度に優れた高速インターフェースが必要です. 従来のパラレル接続ではクロストークやライン数の増加による制約が大きく,次世代の接続規格が求められていました.

JESD204規格の登場とその意義

JESD204は,JEDECが策定したシリアル・データインターフェース規格です. この規格は,Gbps級の高速A-D/D-AコンバータとFPGA/ASIC間をシンプルかつ効率的に接続する目的で開発されました. JESD204は,次のような特徴をもちます.

- Gbps級の伝送速度に対応

- シリアル伝送により配線本数が少ない

- レーン(Lane)構成によって拡張可能

- 高速クロックの同期に対応するフレーミング機構を備える

このように,JESD204はPCI ExpressやUSBといったほかの高速シリアルI/Fに似た特徴をもちつつ,データ変換専用の要件に特化した設計がなされています.

まとめ

JESD204は,アナログ信号の高速ディジタル変換と演算処理をシームレスにつなぐ重要なインターフェースです. 高解像度かつ高速なデータ変換が一般化する中で,Gbps級の信号を安定かつ効率的に取り扱うための鍵となる技術といえます.

JESD204とは何か

JESD204は,JEDEC Solid State Technology Associationによって定められた,高速シリアル・データ伝送規格です. A-DコンバータやD-AコンバータとFPGA/CPUなどの間で,大容量のディジタル信号を安定してやり取りするために設計されました. 「JESD」は「Joint Electron Device Engineering Council Standard」の略称です.

JESD204の世代構成と特徴

JESD204規格には複数のバージョンがあり,用途に応じて進化しています.

- JESD204A:最初のバージョンで,ビットレートは最大3.125Gbps

- JESD204B:レーンのマルチ化に対応し,最大12.5Gbpsのビットレートに拡張

- JESD204C:さらなる高速化が図られ,最大32Gbpsまで対応

特筆すべきはJESD204Cの変換効率です. 従来の8ビット/10ビット変換(効率80%)に代わり,スクランブル方式により最大97%の伝送効率を実現しています. また,伝送単位は66ビットや80ビットとなり,64ビットの実データに2~16ビットの制御情報を加える構造です.

JESD204がもたらす実装上の利点

JESD204は,以下の利点をシステム設計にもたらします.

- レーン構成を柔軟に設定できるため,スケーラビリティに優れる

- 配線本数が削減され,基板設計が容易になる

- ジッタやクロストークの影響を受けにくく,長距離伝送に向いている

- 同期・フレーミングの自動化により複雑な制御が不要

高速ディジタル処理時代において,JESD204はアナログとディジタルをつなぐ重要な技術インフラです. より大規模かつ多チャネルの計測・制御装置において,その価値はますます高まっています.

まとめ

JESD204は,高速A-DコンバータやD-Aコンバータと演算装置を効率よく接続するための規格です. マルチレーン構成や高変換効率により,高信頼なデータ転送を支える鍵となる技術です. 〈著:ZEPマガジン〉

著者紹介

- 1979年 芝浦工業大学 通信工学科卒業

- 同年 Analog Devices of Japan Inc に入社(後にアナログ・デバイセズ株式会社)同社にてアナログ・モジュール開発,Mixedシグナル・テスタのテスト・モジュール開発、高速リニア・カスタム集積回路の開発サポート,汎用リニア製品マーケティング等を担当.

著書

- OPアンプ増幅回路の2つのゲイン,ZEPエンジニアリング株式会社.

- [VOD]高速&エラーレス!5G×EV時代のプリント基板&回路設計 100の要点,ZEPエンジニアリング株式会社.

- [VOD]アナログ・デバイセズの電子回路教室【差動信号とその周辺回路設計技術】,ZEPエンジニアリング株式会社.

- [VOD]アナログ・デバイセズの電子回路教室【A-D/D-Aコンバータの使い方】,ZEPエンジニアリング株式会社.

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

参考文献

- [VOD]Before After!ハイパフォーマンス基板&回路設計 100の基本【パワエレ・電源・アナログ編】/【IoT・無線・通信編】,ZEPエンジニアリング株式会社.

- [VOD]高精度アナログ計測回路&基板設計ノウハウ,ZEPエンジニアリング株式会社.

- [VOD]Gbps超 高速伝送基板の設計ノウハウ&評価技術,ZEPエンジニアリング株式会社.

- [VOD]事例に学ぶ放熱基板パターン設計 成功への要点,ZEPエンジニアリング株式会社.

- [VOD/KIT]GPSクロック・ジッタ・クリーナ,ZEPエンジニアリング株式会社.

- [Book]電子回路とプリント基板のノイズ解決 即答200,ZEPエンジニアリング株式会社.