ZEPマガジン

|

2025年8月11日号

[無線/通信/高周波][基板/実装/3Dプリンタ]

直交IF変調ADMV1013の動作 低エラー・レート広帯域SDR入門 アナログ直交変調IC ADMV1013は,IF入力とベースバンド入力の切り替え機能を備え,動作帯域は0.8GHzから6GHzと広い.4段階の内蔵フィルタでスプリアスを抑制できる |

|

2025年8月10日号

[無線/通信/高周波][基板/実装/3Dプリンタ]

直交IF復調ADMV1014の動作 低エラー・レート広帯域SDR入門 直交復調IC ADMV1014を用いることで,広帯域での低エラー・レート通信が可能になる.RFレベルの自動補償が可能なため,AGCも不要 |

|

2025年8月9日号

[無線/通信/高周波][基板/実装/3Dプリンタ]

ミリ波伝送線路コプレーナの設計 低エラー・レート広帯域SDR入門 上下方向にもグラウンド層をもつ複合型コプレーナは,高周波デバイスとの接続がしやすく,またコネクタ実装時の電気的安定性を確保する上でも有利 |

|

2025年8月8日号

[無線/通信/高周波][基板/実装/3Dプリンタ]

高分離度&低ロス!1.6G~11GHzパワー・ディバイダ 低エラー・レート広帯域SDR入門 ウィルキンソン・ディバイダは,高周波信号を2つに分配するマイクロ波回路.入力信号は等分に分配され,各出力ポートには約-3dBのパワーが到達する |

|

2025年8月7日号

[基板/実装/3Dプリンタ][高速データ伝送/USB][シミュレータ/ツール]

数十kHzの低周波電磁界 3相モータ・インバータの場合 電磁界シミュレータ入門 CST Studioで3次元解析 PWMによる駆動においても,三相ラインを個別にシールドするのではなく,空間的に一体化した構造でのシールドが望ましい |

|

2025年8月6日号

[基板/実装/3Dプリンタ][高速データ伝送/USB][シミュレータ/ツール]

10Gbps信号の電磁界空間放射 電磁界シミュレータ入門 CST Studioで3次元解析 直線的な配線では放射が少なく抑えられる傾向があるが,配線を屈曲させた構造にすると,共振やアンテナ作用により放射が増す |

|

2025年8月5日号

[基板/実装/3Dプリンタ][高速データ伝送/USB][シミュレータ/ツール]

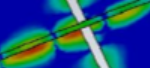

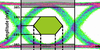

差動信号はスリットを上手に超える 電磁界シミュレータ入門 CST Studioで3次元解析 スリット部を通過する際,差動伝送を用いると,信号の一部はスリット側に逃げるものの,大部分のエネルギは減衰せずに伝送される |

|

2025年8月4日号

[基板/実装/3Dプリンタ][高速データ伝送/USB][シミュレータ/ツール]

キャパシタでスリット超え リターン経路は絶対確保 電磁界シミュレータ入門 CST Studioで3次元解析 スリットによるリターン経路の断絶は,近傍にキャパシタを配置することである程度補うことが可能 |

|

2025年8月3日号

[基板/実装/3Dプリンタ][高速データ伝送/USB][シミュレータ/ツール]

高速信号のスリットまたぎ 電磁界シミュレータ入門 CST Studioで3次元解析 高速信号ならスリットをうまく通過できるように見えるが,実際は信号のエネルギの一部がスリット方向に流出する |

|

2025年8月2日号

[基板/実装/3Dプリンタ][高速データ伝送/USB][シミュレータ/ツール]

30Gbps/0.03ns!超高速パルスの波形観測 電磁界シミュレータ入門 CST Studioで3次元解析 直流と異なり,高周波のリターン電流は伝送路全体を経由するのではなく,信号の進行に伴って同方向に進む |

|

2025年8月1日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

JESD伝送路の設計基礎と差動伝送 計測のためのA-Dコンバータ実装術 JESDインターフェースの評価試験は,FPGAや各種ソフトウェアに組み込まれたサポート機能を用いて実施する |

|

2025年7月31日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

JESDトランシーバの評価法 計測のためのA-Dコンバータ実装術 FPGAの開発環境に組み込まれているアイ・パターン観測用ツールを利用することで,実機での評価を補完し,より詳細な解析が可能 |

|

2025年7月30日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

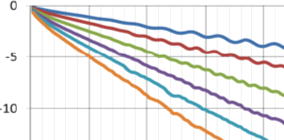

FR4基板とストリップ線路の特性 計測のためのA-Dコンバータ実装術 10Gbps以上の高速信号では,-5dBまで損失が増すため信号品質が規格を満たさない可能性がある |

|

2025年7月29日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

JESD204におけるリターン・ロスの意味と役割 計測のためのA-Dコンバータ実装術 リターン・ロスが大きいほど入力信号が反射せずに伝送されていることを意味する.理想は,S11はゼロ,リターン・ロスはマイナス無限大 |

|

2025年7月28日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

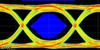

高速シリアル・インターフェースの評価指標「アイ・パターン」 計測のためのA-Dコンバータ実装術 Sパラメータで表されるS21の挿入損失,ケーブルによる周波数依存性のロス,信号の反射によるひずみは,信号のタイミングに影響し,ビット・エラーの原因になる |

|

2025年7月27日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

JESD204における伝送路ロスと波形補正の重要性 計測のためのA-Dコンバータ実装術 Sパラメータで表される$S_{21}$の挿入損失,ケーブルによる周波数依存性のロス,信号の反射によるひずみは,信号のタイミングに影響し,ビット・エラーの原因になる |

|

2025年7月26日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

CMLとLVDSの送信回路の共通点と違い 計測のためのA-Dコンバータ実装術 高速A-Dコンバータの送信回路の代表は,CML(Current Mode Logic)とLVDS(Low Voltage Differential Signaling).両者は,高速性と低ノイズ特性を備える差動伝送方式 |

|

2025年7月25日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

JESD204通信における専用線の役割 計測のためのA-Dコンバータ実装術 JESD204の通信では,データ転送に使用される信号線とは別に,制御や同期のための専用線が存在する |

|

2025年7月24日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

JESD204のレーン構成と信号方向 計測のためのA-Dコンバータ実装術 JESD204は,A-Dコンバータの高速化と高精度化の要求に対応するシリアル通信規格.特にJESD204BやJESD204Cが広く用いられている |

|

2025年7月23日号

[アナログ/センサ/計測][基板/実装/3Dプリンタ]

LVDSからJESD204BCまで!高速ADC I/Fの伝送速度 計測のためのA-Dコンバータ実装術 高速A-Dコンバータを用いれば,ミキシングや波形合成などのRF信号処理もディジタル領域で実行でき,アナログ回路の温度による特性変化や経年劣化を克服できる |