ZEPマガジン

|

2025年12月9日号

[アナログ/センサ/計測][シミュレータ/ツール][測定器/分析装置]

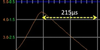

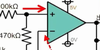

位相補償容量の最適値探し:電子回路シミュレーションで実験 位相遅れと補償容量の関係 補償用キャパシタの容量が小さいと安定性の改善は限定的.容量が大きすぎると過補償となり,応答速度が低下したり波形のひずみが発生したりする |

|

2025年12月8日号

[アナログ/センサ/計測][シミュレータ/ツール][測定器/分析装置]

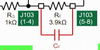

増幅回路の発振を止める:定石「進み位相補償」 増幅回路の発振とその原因 増幅回路の出力信号が入力に逆相で戻る際,十分な位相余裕がないと,信号が自己増幅されて周期的に振動する.この好ましくない現象を抑えるために,位相補償が有効 |

|

2025年12月7日号

[アナログ/センサ/計測][シミュレータ/ツール][測定器/分析装置]

増幅回路の出力インピーダンス:負帰還による抑圧効果 増幅回路の出力インピーダンスとは 増幅回路における出力インピーダンスは,回路の出力端から見た内部のインピーダンス.単体のOPアンプは数百Ωから数kΩの値をもつ |

|

2025年12月6日号

[アナログ/センサ/計測][シミュレータ/ツール][測定器/分析装置]

増幅回路の誤差「オフセット電圧」の設計法 OPアンプのオフセット電圧のモデリング OPアンプの増幅回路におけるオフセット電圧は,入力端子に印加された電圧差がゼロであっても,出力に現れる誤差のこと |

|

2025年12月5日号

[アナログ/センサ/計測][シミュレータ/ツール][測定器/分析装置]

大振幅と小振幅で全然違う!増幅回路の周波数特性 小振幅時の周波数特性を決めるGBW,大振幅時の周波数特性を決めるスルーレート OPアンプ増幅回路は,周波数が高くなるほど出力信号が縮んでいく性質がある.小さな信号ではゲイン帯域幅GBWで説明できるが,入力振幅が大きい場合は別の制限が支配的になる |

|

2025年12月4日号

[アナログ/センサ/計測][シミュレータ/ツール][測定器/分析装置]

高域でのゲイン低下に注意!OPアンプ増幅回路の周波数特性 OPアンプ増幅回路の周波数特性とは OPアンプ増幅回路は低域では抵抗で設定したゲインとおりの特性が得られるが,周波数が上がるにつれてゲインが低下し始める |

|

2025年12月3日号

[アナログ/センサ/計測][シミュレータ/ツール][測定器/分析装置]

入力と出力の電圧が等しい…それでもアンプ?絶対使う「ボルテージ・フォロア」 実験キットとパソコンで学ぶアナログ電子回路教室 ゲイン1倍のアンプ「ボルテージ・フォロワ」は,高い信号源抵抗をもつセンサなどの電圧信号を低インピーダンスの負荷に正確に伝えることができる |

|

2025年12月2日号

[アナログ/センサ/計測][シミュレータ/ツール][測定器/分析装置]

USBマルチ測定器ADALM1000用測定アプリ ALICEのPCセットアップ ダウンロード/インストールからUSB認識/起動まで ALICEはADALM1000を操作するための専用GUIソフトウェア.波形表示,直流・交流の信号生成,I-V測定,データ記録などの機能を備える |

|

2025年12月1日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

[PR]トランジスタの増幅作用:キットで学ぶ電子回路設計 トランジスタの増幅作用とI-V特性の理解 トランジスタのふるまいの理解は,電子回路設計の基礎を身につけるために重要.PC制御のUSBテスタでトランジスタを動かして,その基礎を身に付けよう |

|

2025年11月30日号

[信号処理/セキュリティ][電磁気/数学/統計/力学]

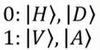

量子鍵の基本的な転送プロトコルBB84とは 量子技術が変える次世代サイバ・セキュリティ 量子状態で情報を表現する量子ビットは,重ね合わせやもつれの特性をもつ.この性質を活用することで,従来の暗号アルゴリズムでは困難だった安全性の確保が可能 |

|

2025年11月29日号

[AI/IoT/マイコン][ロボット/自動運転/宇宙]

停止中の車が急加速!?CANになりすまし攻撃 実車で確認されたCANなりすましの実際 送信エラーの累積によってノードが自己隔離する「バスオフ」は,故障耐性を目的とした規定動作.復帰には一定の条件や手続きが必要 |

|

2025年11月28日号

[信号処理/セキュリティ][電磁気/数学/統計/力学]

量子技術が変える次世代サイバ・セキュリティ 量子論の基礎から量子鍵配送プロトコルBB84まで 量子状態で情報を表現する量子ビットは,重ね合わせやもつれの特性をもつ.この性質を活用することで,従来の暗号アルゴリズムでは困難だった安全性の確保が可能 |

|

2025年11月27日号

[AI/IoT/マイコン][ロボット/自動運転/宇宙]

実車実験!車載CANへのなりすまし攻撃 車載CANのプロトコル解析 送信エラーの累積によってノードが自己隔離する「バスオフ」は,故障耐性を目的とした規定動作.復帰には一定の条件や手続きが必要 |

|

2025年11月26日号

[信号処理/セキュリティ][AI/IoT/マイコン]

600GOPS!STM32N6マイコンによるエッジAIカメラの開発 Cortex-M55で動かすセキュア・ファームウェア Cortex-M55上で動かすファームウェアは,セキュア・ブートとハードウェア・アクセラレータによる暗号化機能を組み合わせて作る |

|

2025年11月25日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

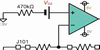

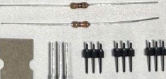

1度は必ず見舞われる定番トラブル「発振」と対策 実験キットで学ぶ初歩電子回路設計 発振は位相補償を適切に施すことで安全に制御できる.回路の寄生素子や信号遅延を理解し,小容量のキャパシタを追加することで対策できる |

|

2025年11月24日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

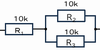

脱教科書!設計者が使う定数E24系列 実験キットで学ぶ初歩電子回路設計 E24系列は,基本的な抵抗値を24段階に分けて定義したもので,1.0,1.1,1.2から9.1までの数字が2桁の基本値として設定されている |

|

2025年11月23日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

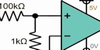

非反転バッファや単電源アンプにレール・ツー・レールOPアンプ 実験キットで学ぶ初歩電子回路設計 レール・ツー・レールOPアンプは,入力端子や出力端子が電源電圧に非常に近い範囲で動作可能な信号増幅用アナログIC |

|

2025年11月22日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

バイポーラとFETどうやって使いわける? 実験キットで学ぶ初歩電子回路設計 バイポーラ・トランジスタは,ベースに流す電流に応じてコレクタ電流が増幅される.FETはゲートに加える電圧でドレイン-ソース間を制御する |

|

2025年11月21日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

トランジスタを動かす電流増幅の実験 実験キットで学ぶ初歩電子回路設計 トランジスタの動作によって,ベース電流に応じてコレクタ電流が増幅される.この特性を利用することで,スイッチやアンプを実現できる |

|

2025年11月20日号

[アナログ/センサ/計測][半導体/電子部品][AI/IoT/マイコン]

USB半導体チェッカを動かす実習の準備 実験キットで学ぶ初歩電子回路設計 キット付きVOD教材「実験キットで学ぶ初歩の電子回路設計」に付属するUSB半導体チェッカを使う前に,電源供給や接続環境を確認する |